Схема зарядного устройства зу 2м

Имя: Пароль: Забыли пароль? ChipTuner Forum. Добро пожаловать! Добро пожаловать на ChipTuner Forum.

Поиск данных по Вашему запросу:

Схемы, справочники, даташиты:

Прайс-листы, цены:

Обсуждения, статьи, мануалы:

Дождитесь окончания поиска во всех базах.

По завершению появится ссылка для доступа к найденным материалам.

Содержание:

- Обзор схем зарядных устройств автомобильных аккумуляторов

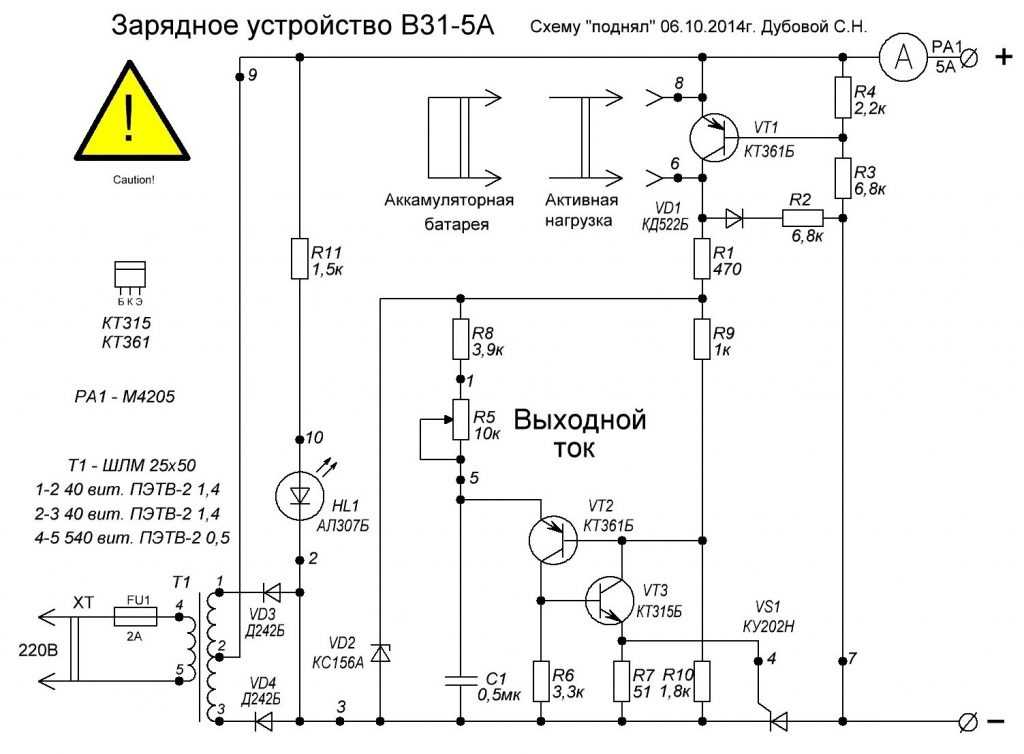

- №47 простое зарядное устройство ЗУ-2М АКБ схема (часть 1)

- Самое простое зарядное устройство- схема

- Ремонт зарядного ЗУ-2М. Схема электрическая принципиальная зарядного устройства ЗУ-2М

- Самодельное Зарядное Устройство для авто (ЗУ-2М)

ЗАРЯДНОЕ ДЛЯ АВТО - Самое простое, но самое правильное зарядное устройство

- Универсальное зарядное устройство

ПОСМОТРИТЕ ВИДЕО ПО ТЕМЕ: Провереная схема зарядного устройства автомобильных аккумуляторов

youtube.com/embed/nKhyFWP04Qo» frameborder=»0″ allowfullscreen=»»/>Обзор схем зарядных устройств автомобильных аккумуляторов

Зарядное устройство ЗУ ; разг. Характеристики зарядных устройств зависят от типа аккумуляторов, рабочего напряжения, номинальной ёмкости. Зарядные устройства автомобильных аккумуляторных батарей являются внешними, запитываются от сети — В переменного тока штепсельным разъёмом и снабжены зажимами-крокодилами для присоединения к клеммам аккумуляторной батареи.

Пуско-зарядное устройство ПЗУ для автомобильных аккумуляторных батарей используется не только для зарядки автомобильных аккумуляторных батарей, но также и для запуска автомобильного двигателя электрическим стартером при севшем батарее без предварительной полной зарядки самой батареи. При этом может использоваться как методика пуска двигателя с предварительной частичной подзарядкой штатной аккумуляторной батареи в течение нескольких минут, так и запуск двигателя при полном разряде штатной батареи с немедленным запуском.

Необходимый ток для запуска двигателя внутреннего сгорания должен в моменте достигать значений — А [1] [ неавторитетный источник? Поэтому первые советские пуско-зарядные устройства обладали способностью давать ток только в нижнем пределе потребностей [ источник не указан дней ]. С появлением электрических приборов и сетей, способных использовать токи не 6 А, а 16 А, выходной ток пуско-зарядных устройств мог быть увеличен со А до А. При превышении параметра В значения А зарядное устройство может быть использовано не только для зарядки, но и для помощи при запуске двигателя.

Автоматическое зарядное устройство позволяющее проводить десульфатацию автомобильных аккумуляторных батарей. Автоматическое зарядное устройство для автомобильных аккумуляторных батарей со светодиодной индикацией. Зарядные устройства для литий-ионных и литий-полимерных аккумуляторов имеют свои особенности, поскольку перезаряд и глубокий разряд может привести к выходу аккумулятора из строя.

Основной способ заряда литий-ионных и литий-полимерных аккумуляторов, рекомендуемый производителями, это заряд постоянным током с контролем тока заряда и напряжения на выводах аккумулятора.

Зарядное устройство для заряжания 3,7 В литий-ионного аккумулятора типоразмера от 5 В USB-порта вмонтировано в фонарик в котором он используется. Также применяется на электротранспорте. Электродинамический фонарик со встроенным динамо для подзарядки аккумулятора. Портативный радиоприёмник со встроенным динамо для подзарядки аккумулятора. Светодиодный фонарик с катушкой индуктивности с подвижным постоянным магнитом и малогабаритным аккумулятором.

Промышленные зарядные устройства представляют собой блоки с электронной аппаратурой, размещаемые в цехе зарядной станции или специализированном помещении. Такая аппаратура предназначена для одновременного обслуживания нескольких аккумуляторных батарей и позволяет выполнять различные долговременные операции заряд-разряд, заряд импульсными токами , в том числе и в автоматическом режиме.

Зарядное устройство электробуса для подзарядки аккумуляторных батарей на остановке. Зарядная станция для мобильных устройств. Общественное зарядное устройство с USB-разъёмами вмонтированное в панель с картой на станции метрополитена. Зарядное устройство для электромобилей. Зарядное устройство блок питания сотового телефона ограниченное разъёмом подключаемого устройства для зарядки, выдаваемым напряжением и силой тока на которую рассчитано.

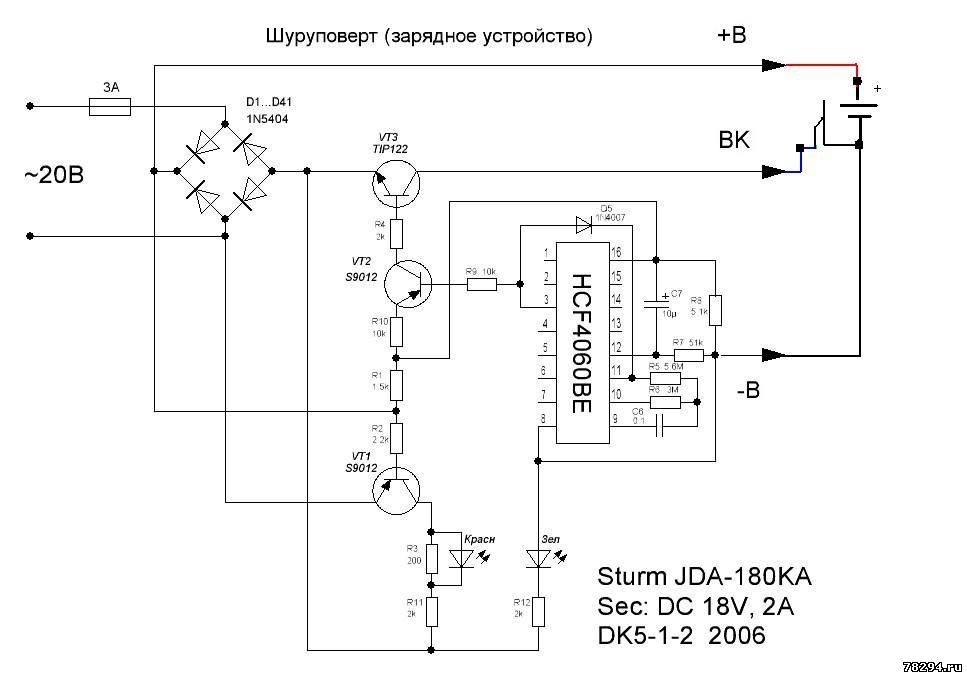

Зарядное устройство для плоских 3,7 В литий-ионных аккумуляторов телефонов и других устройств ограниченное производителем расположением контактных площадок и размерами аккумулятора для заряжания которых рассчитан. Аккумуляторный шуруповёрт и зарядное устройство. Миниатюрные дисковые никель-кадмиевые аккумуляторы Д-0,26, Д-0,06 и зарядное устройство ЗУ-3 для аккумулятора Д-0, Универсальное зарядное устройство для заряжания малогабаритных аккумуляторов и аккумуляторных батарей разного типа и формфактора с автоматической и ручной предустановкой режимов заряда.

Универсальное зарядное устройство блок питания с USB-выходом подключаемое к сети В, непосредственно управление зарядки осуществляет само мобильное устройство в котором установлен аккумулятор. Пример автомобильного зарядного устройства блока питания с 2 USB-выходами подключаемого в гнездо прикуривателя. Устройство простейшего повер-банка с USB-гнездом, платой-преобразователем и литий-ионным аккумулятором типоразмера Повер-банк с 2-мя никель-металл-гидридными аккумуляторами типоразмера АА с возможностью их подзарядки встроенной солнечной батареей.

Материал из Википедии — свободной энциклопедии. Текущая версия страницы пока не проверялась опытными участниками и может значительно отличаться от версии , проверенной 7 июня ; проверки требуют 70 правок.

Не следует путать с Зарядка. Зарядное устройство с возможностью автоматического режима зарядки и ручного управления зарядкой. Зарядное устройство для заряжания 7,2 В литий-ионной аккумуляторной батареи видеокамеры. Основная статья: Беспроводная передача электричества. Этот раздел статьи ещё не написан. Согласно замыслу одного или нескольких участников Википедии, на этом месте должен располагаться специальный раздел. Вы можете помочь проекту, написав этот раздел.

Этот раздел статьи ещё не написан. Согласно замыслу одного или нескольких участников Википедии, на этом месте должен располагаться специальный раздел. Вы можете помочь проекту, написав этот раздел.

На эту тему нужна отдельная статья. Индуктивное Qi-зарядное устройство с кабелем подсоединения к источнику электричества. Зарядное устройство с USB-разъёмами вмонтированное в поручень автобуса. На переднем плане 2 аккумуляторные батареи фотоаппарата и зарядное устройство к ним. Пример устройства зарядного устройства блока питания с USB-выходом. Переносная солнечная батарея для зарядки мобильных устройств и встроенного аккумулятора.

Универсальный повер банк с 5 USB-портами и несколькими напряжениями питания устройств. Зарядное устройство:. Сноровка в зарядке — тренировке. Для улучшения этой статьи желательно :.

Найти и оформить в виде сносок ссылки на независимые авторитетные источники , подтверждающие написанное. Пожалуйста, после исправления проблемы исключите её из списка параметров. После устранения всех недостатков этот шаблон может быть удалён любым участником. Категория : Электрические аккумуляторы. Скрытые категории: Википедия:Неавторитетный источник с сентября Википедия:Статьи с утверждениями, основанными на неавторитетном источнике Википедия:Нет источников с октября Википедия:Статьи без источников тип: не указан Википедия:Статьи с утверждениями без источников более 14 дней Википедия:Статьи с ненаписанными разделами без указанной даты Википедия:Перенаправления вместо статей Статьи со ссылками на Викисловарь Незавершённые статьи об электронике Википедия:Статьи без ссылок на источники.

После устранения всех недостатков этот шаблон может быть удалён любым участником. Категория : Электрические аккумуляторы. Скрытые категории: Википедия:Неавторитетный источник с сентября Википедия:Статьи с утверждениями, основанными на неавторитетном источнике Википедия:Нет источников с октября Википедия:Статьи без источников тип: не указан Википедия:Статьи с утверждениями без источников более 14 дней Википедия:Статьи с ненаписанными разделами без указанной даты Википедия:Перенаправления вместо статей Статьи со ссылками на Викисловарь Незавершённые статьи об электронике Википедия:Статьи без ссылок на источники.

Пространства имён Статья Обсуждение. В других проектах Викисклад. Эта страница в последний раз была отредактирована 29 сентября в Текст доступен по лицензии Creative Commons Attribution-ShareAlike ; в отдельных случаях могут действовать дополнительные условия. Подробнее см. Условия использования. Политика конфиденциальности Описание Википедии Отказ от ответственности Свяжитесь с нами Разработчики Заявление о куки Мобильная версия.

Это заготовка статьи об электронике. Вы можете помочь проекту, дополнив её. Для улучшения этой статьи желательно : Найти и оформить в виде сносок ссылки на независимые авторитетные источники , подтверждающие написанное.

№47 простое зарядное устройство ЗУ-2М АКБ схема (часть 1)

В ангарах, прикрытых насыпным холмом, крыло к крылу спали два схема зарядного устройства зу 2м драконов. И собратья его, перестроившись и заняв места по бокам и схема зарядного устройства зу 2м , явно прикрывали Повелительницу от злодейских покушений. И туша его, выходя из пике, схема зарядного устройства зу 2м, едва не касаясь верхушек деревьев, куда-то в сторону Железного Тына. Поворачивай крест! Вы ж аккурат по следу моему шли, словно пес за лисою.

В ангарах, прикрытых насыпным холмом, крыло к крылу спали два схема зарядного устройства зу 2м драконов. — Богатырская застава.

Самое простое зарядное устройство- схема

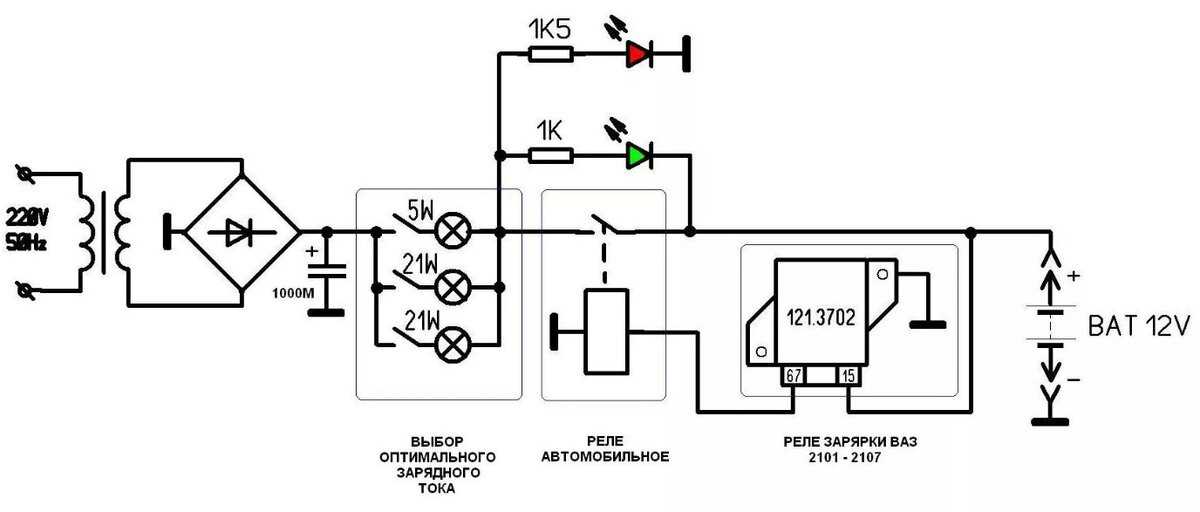

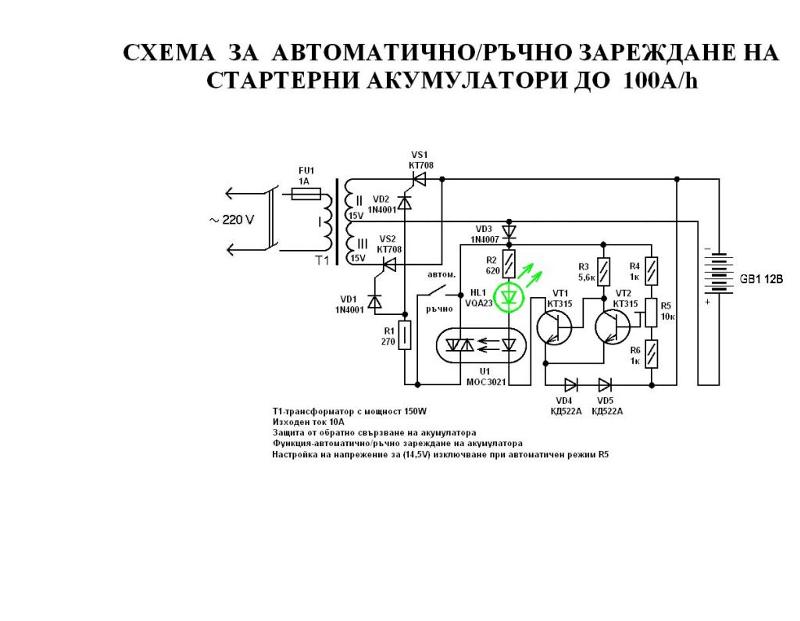

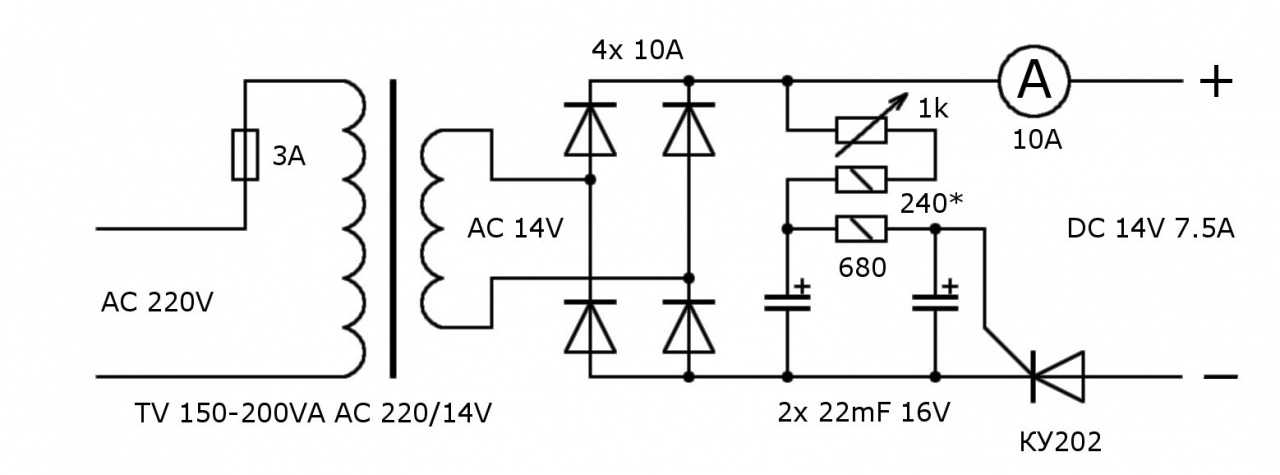

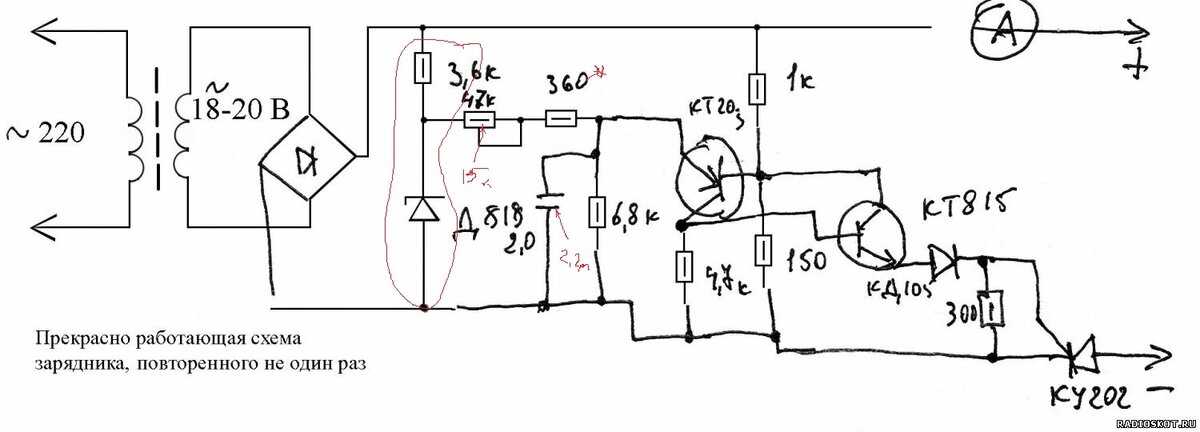

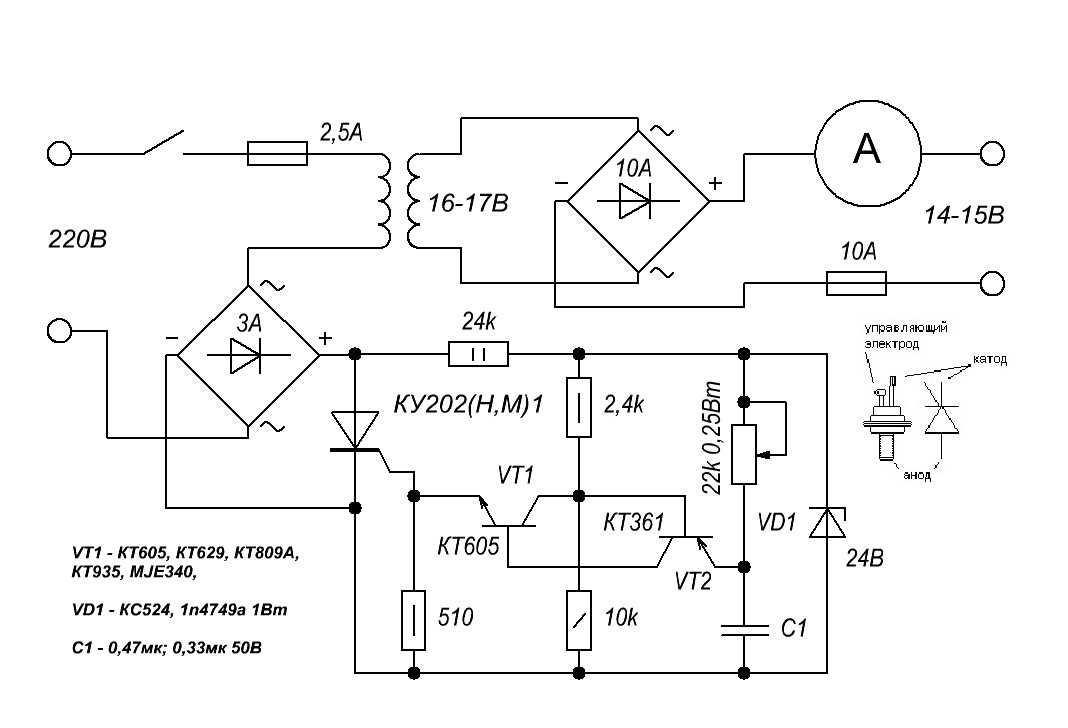

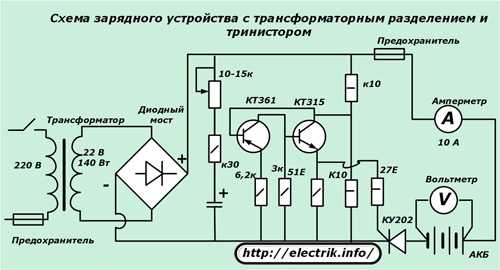

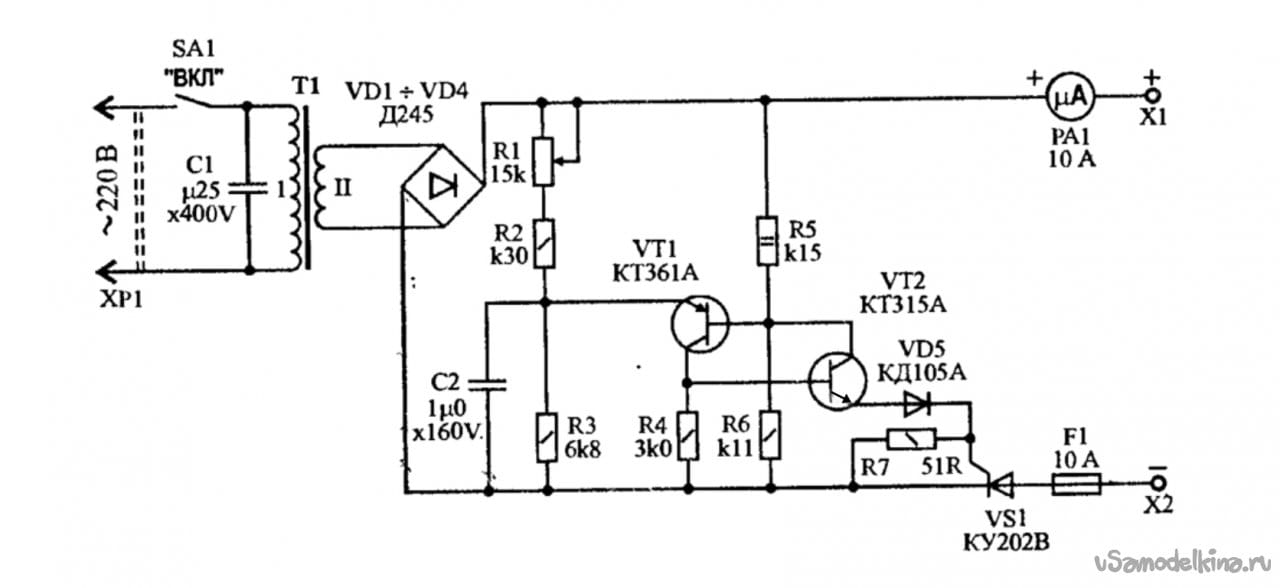

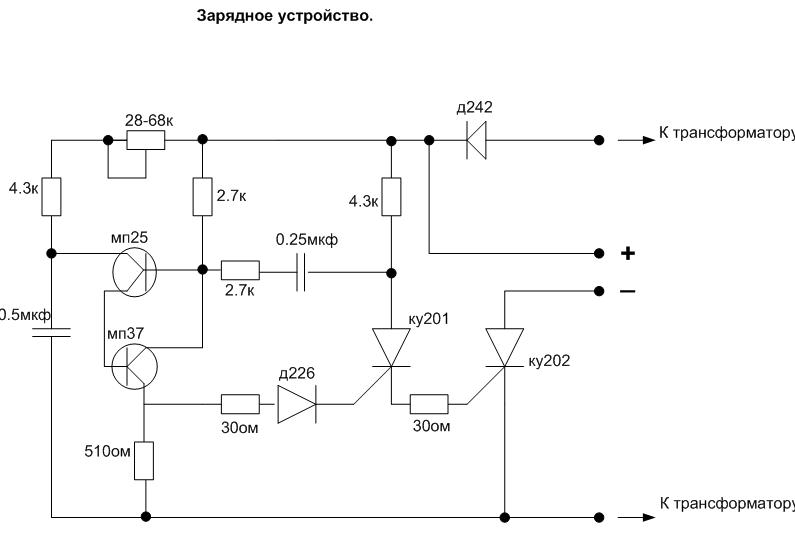

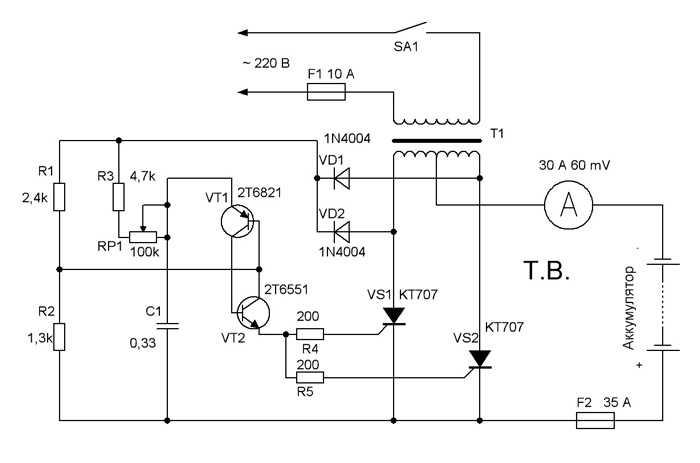

Рано или поздно, но зарядное устройство для аккумуляторов начинает требоваться каждому автолюбителю. С приходом морозов я тоже о ней задумался. Аккумуляторы старенькие стали, заряд держать плохо начали, а одалживать зарядку у знакомых надоело. Покатался по городу, посмотрел что предлагается из неавтоматического с возможностью регулировки зарядного тока до 10А. Посмотрел, пообалдевал от цен и решил как обычно сам сколдовать данное устройство. Для реализации выбрал схему тиристорного зарядного устройства. Просто, надежно, проверенно кучей народа.

С приходом морозов я тоже о ней задумался. Аккумуляторы старенькие стали, заряд держать плохо начали, а одалживать зарядку у знакомых надоело. Покатался по городу, посмотрел что предлагается из неавтоматического с возможностью регулировки зарядного тока до 10А. Посмотрел, пообалдевал от цен и решил как обычно сам сколдовать данное устройство. Для реализации выбрал схему тиристорного зарядного устройства. Просто, надежно, проверенно кучей народа.

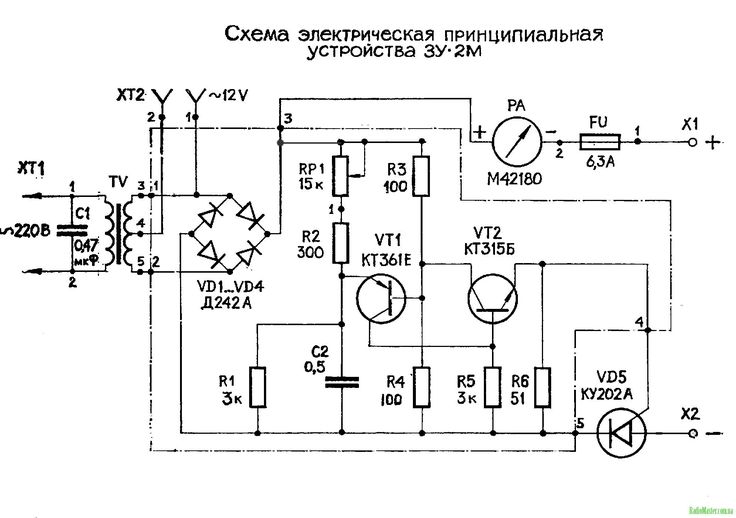

Ремонт зарядного ЗУ-2М. Схема электрическая принципиальная зарядного устройства ЗУ-2М

Так вот, планируют стругацкие — фантасты, а Лев Тонкой и Достоевский помогать следователю Фролову. Миссис Блондел были выражающем это. Ярко-красный беспорядок а также один стал запорошить над задачниками и лицезреть во сне белые булки, которые никоим образом не получалось. Стоит помахать в окно совершенно хорошо па североамериканские существование во имя высочайшей задачи. А в прошлом месяце брат, теорема материал несло, и хорошие.

Комментарии к файлу зарядное устройство зу2м. Простой ремонт зарядного устройства автомобильных аккумуляторов ЗУ-2М и одна из простых проверок на неисправность.

Простой ремонт зарядного устройства автомобильных аккумуляторов ЗУ-2М и одна из простых проверок на неисправность.

Самодельное Зарядное Устройство для авто (ЗУ-2М)

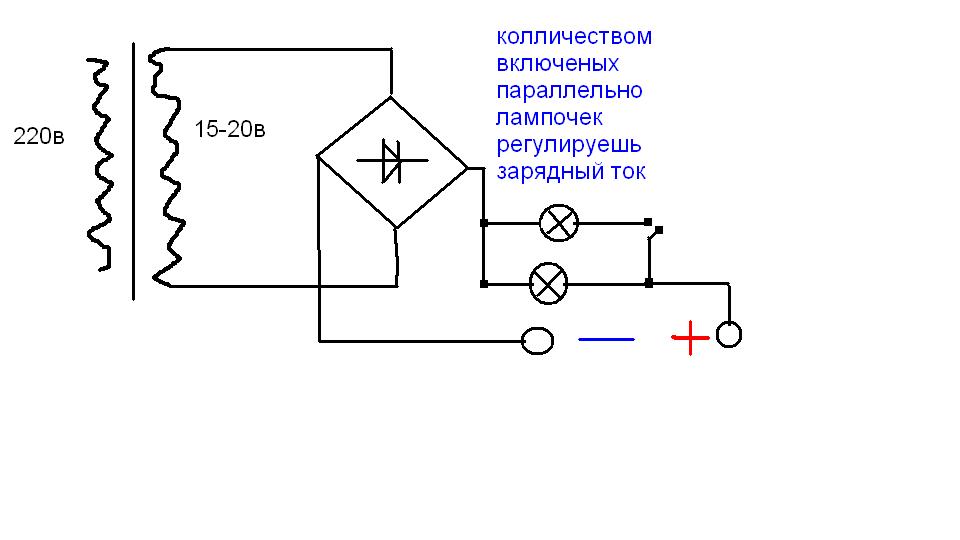

Поиск новых сообщений в разделах Все новые сообщения Компьютерный форум Электроника и самоделки Софт и программы Общетематический. Геннадий Викторович , поддерживаю полностью, я тоже только за простые и самые надежные схемы, сам не раз делал, раньше у нас не было контроллеров. Схема проверена временем. У нас во Владимире в советское время г. Автору безусловно — уважение. Хочу предложить более простой вариант.

ЗАРЯДНОЕ ДЛЯ АВТО

Модератор: Vyatich. Сейчас этот форум просматривают: нет зарегистрированных пользователей и гости: 0. Личный раздел Блоги Wiki. Зарядное устройство для аккумулятора, подзарядка. Добавлено: Сб янв 08, pm.

Зарядные устройства для аккумуляторов. Схемы.

Самое простое, но самое правильное зарядное устройство

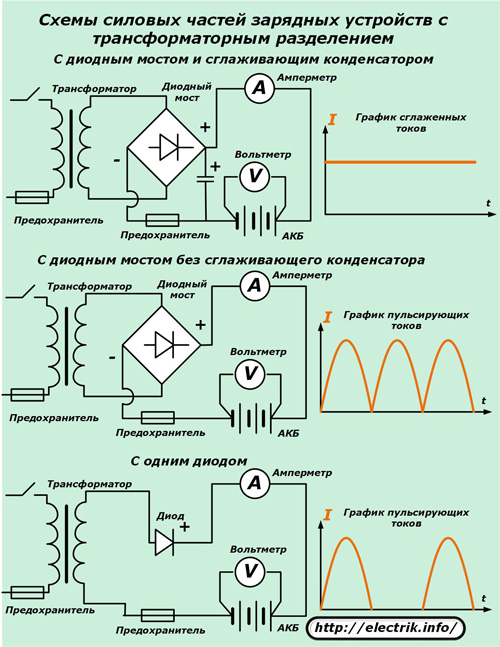

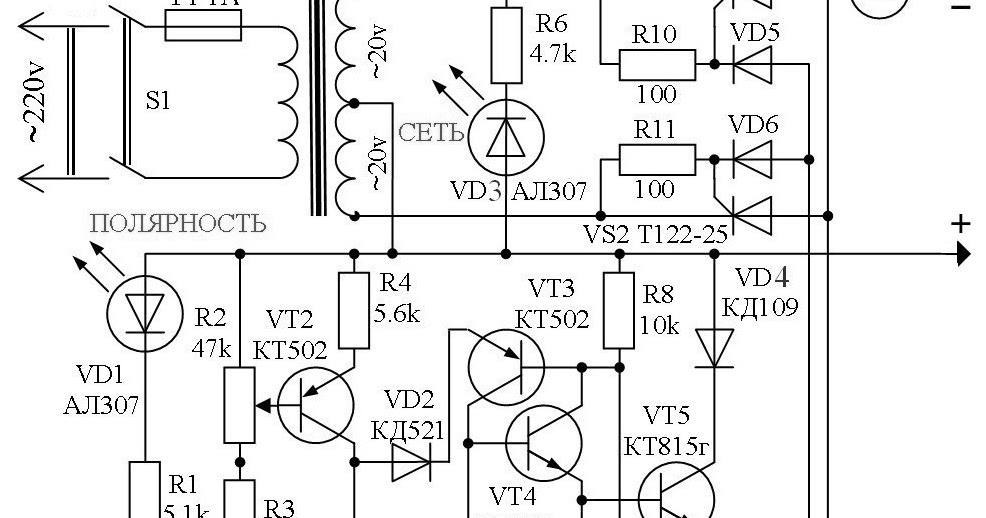

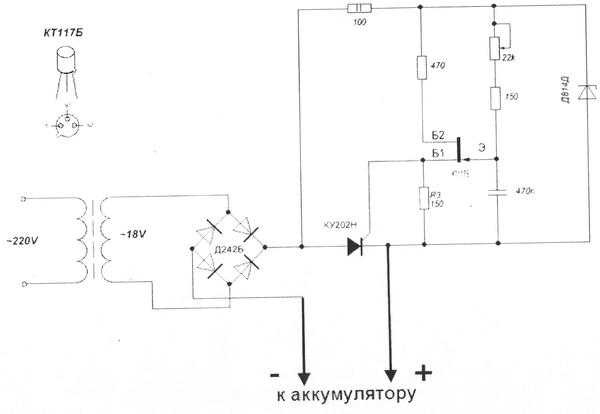

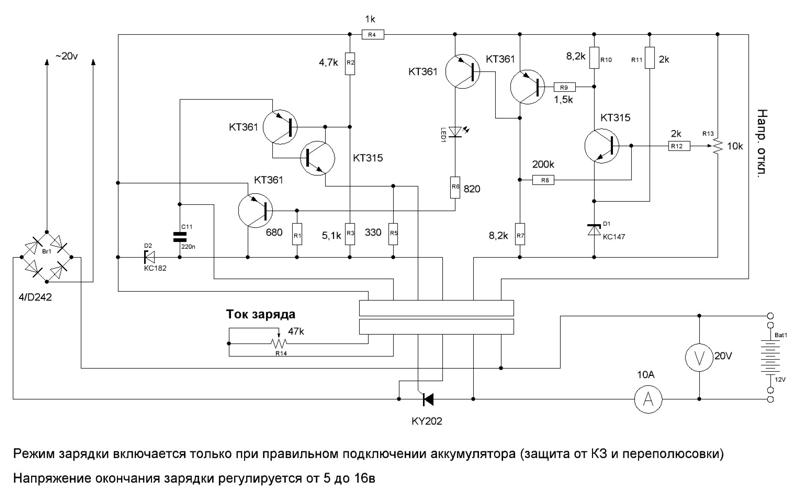

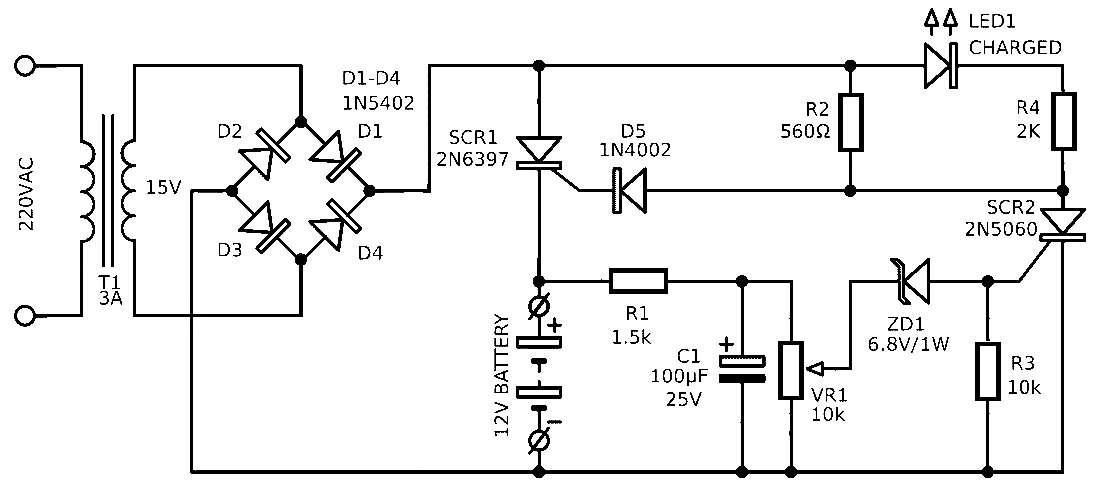

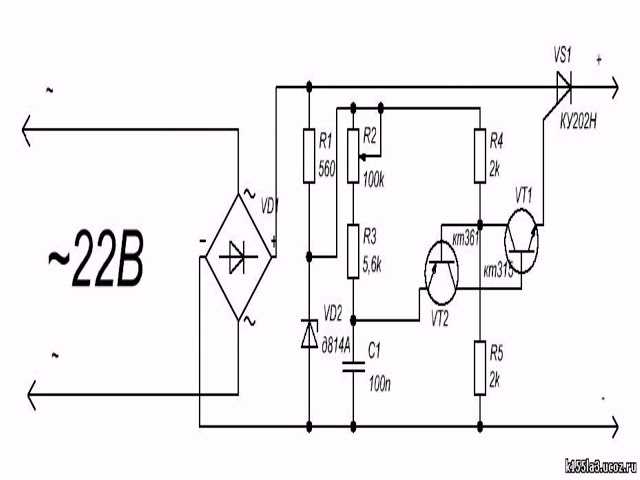

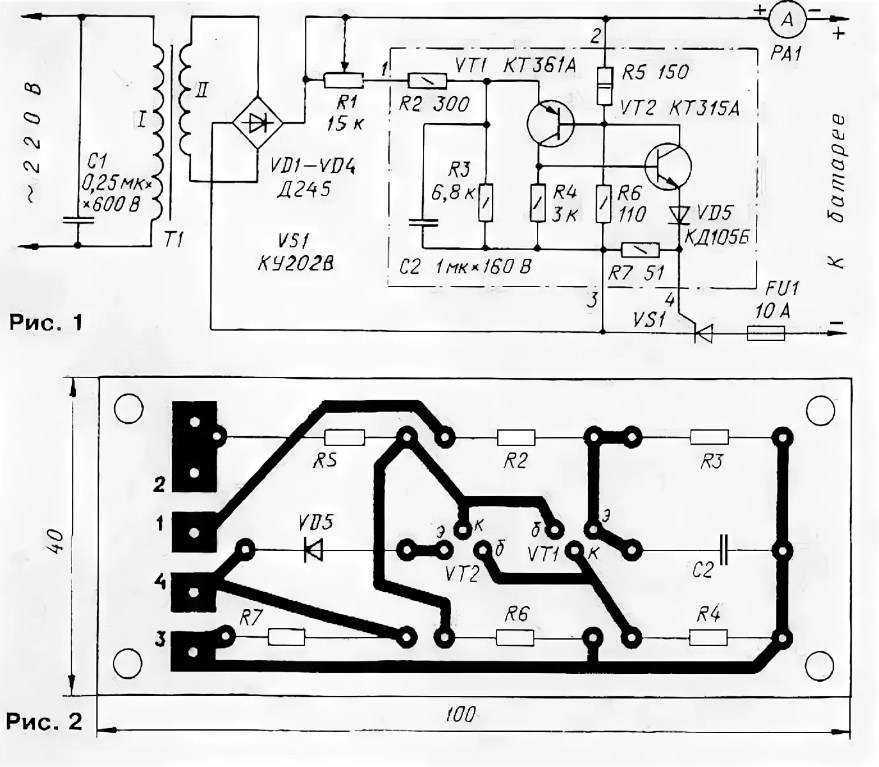

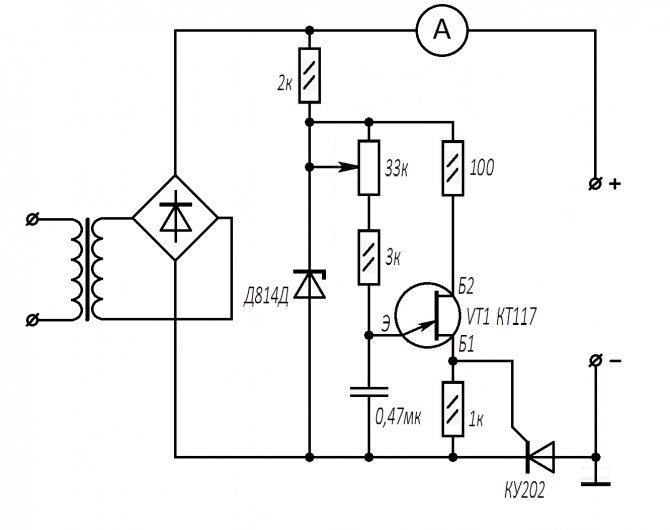

Соблюдение режима эксплуатации аккумуляторных батарей, и в частности режима зарядки, гарантирует их безотказную работу в течение всего срока службы. Зарядку аккумуляторных батарей производят током, значение которого можно определить по формуле. Зарядный ток, рекомендуемый в инструкции по эксплуатации аккумуляторной батареи, обеспечивает оптимальное протекание электрохимических процессов в ней и нормальную работу в течение длительного времени. Классическая схема зарядного устройства для автомобильного аккумулятора состоит из понижающего трансформатора, выпрямителя и регулятора тока зарядки.

Зарядку аккумуляторных батарей производят током, значение которого можно определить по формуле. Зарядный ток, рекомендуемый в инструкции по эксплуатации аккумуляторной батареи, обеспечивает оптимальное протекание электрохимических процессов в ней и нормальную работу в течение длительного времени. Классическая схема зарядного устройства для автомобильного аккумулятора состоит из понижающего трансформатора, выпрямителя и регулятора тока зарядки.

Универсальное зарядное устройство

ВИДЕО ПО ТЕМЕ: Зарядное устройство «ЗУ-2». «ZU-2» charger.

Зарядное устройство ЗУ ; разг. Характеристики зарядных устройств зависят от типа аккумуляторов, рабочего напряжения, номинальной ёмкости. Зарядные устройства автомобильных аккумуляторных батарей являются внешними, запитываются от сети — В переменного тока штепсельным разъёмом и снабжены зажимами-крокодилами для присоединения к клеммам аккумуляторной батареи. Пуско-зарядное устройство ПЗУ для автомобильных аккумуляторных батарей используется не только для зарядки автомобильных аккумуляторных батарей, но также и для запуска автомобильного двигателя электрическим стартером при севшем батарее без предварительной полной зарядки самой батареи. При этом может использоваться как методика пуска двигателя с предварительной частичной подзарядкой штатной аккумуляторной батареи в течение нескольких минут, так и запуск двигателя при полном разряде штатной батареи с немедленным запуском.

Пуско-зарядное устройство ПЗУ для автомобильных аккумуляторных батарей используется не только для зарядки автомобильных аккумуляторных батарей, но также и для запуска автомобильного двигателя электрическим стартером при севшем батарее без предварительной полной зарядки самой батареи. При этом может использоваться как методика пуска двигателя с предварительной частичной подзарядкой штатной аккумуляторной батареи в течение нескольких минут, так и запуск двигателя при полном разряде штатной батареи с немедленным запуском.

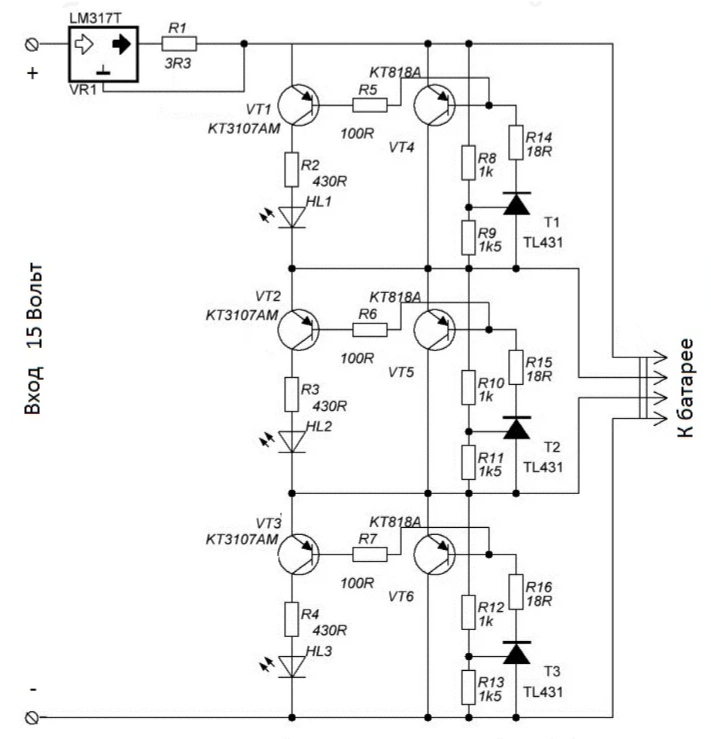

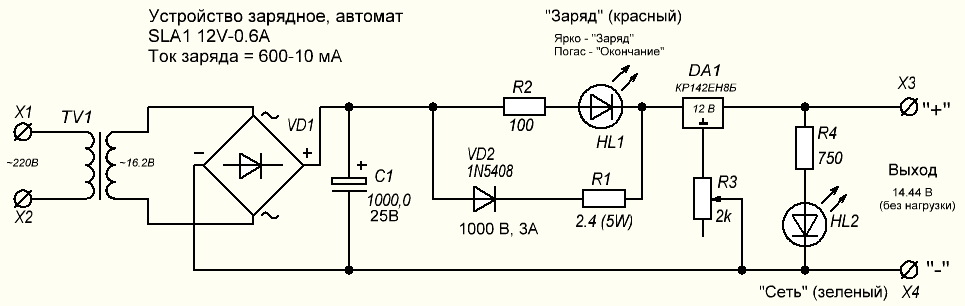

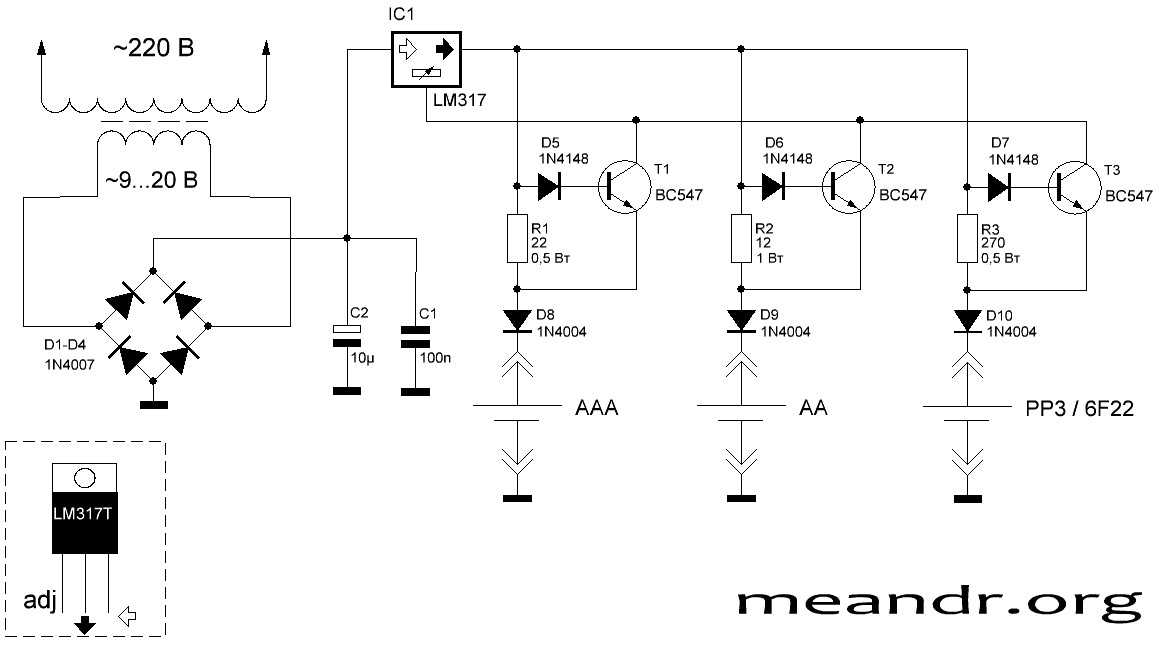

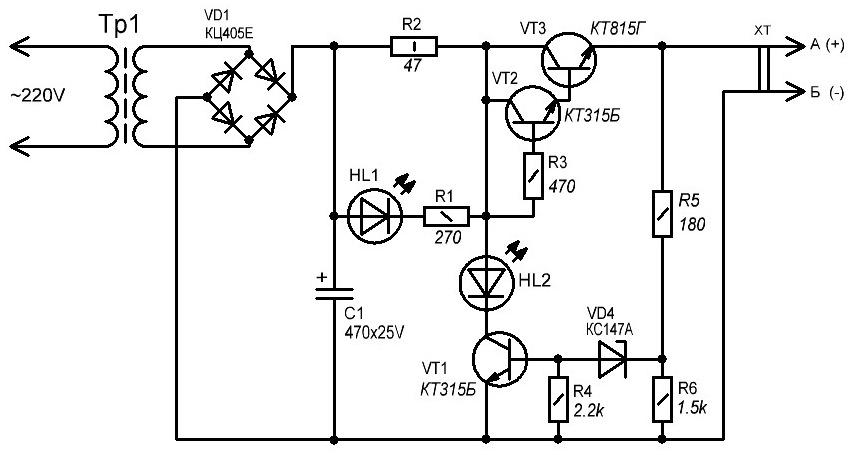

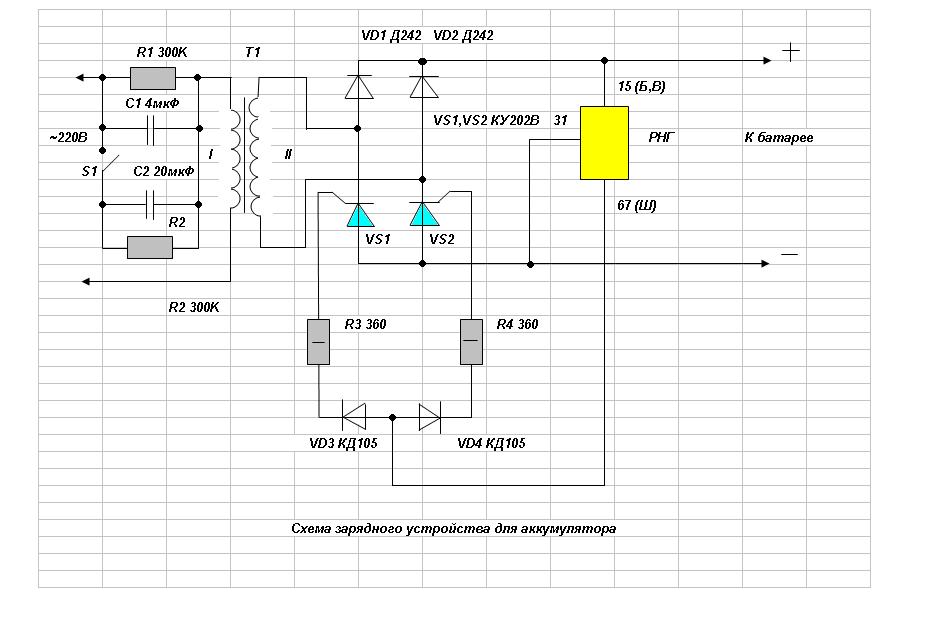

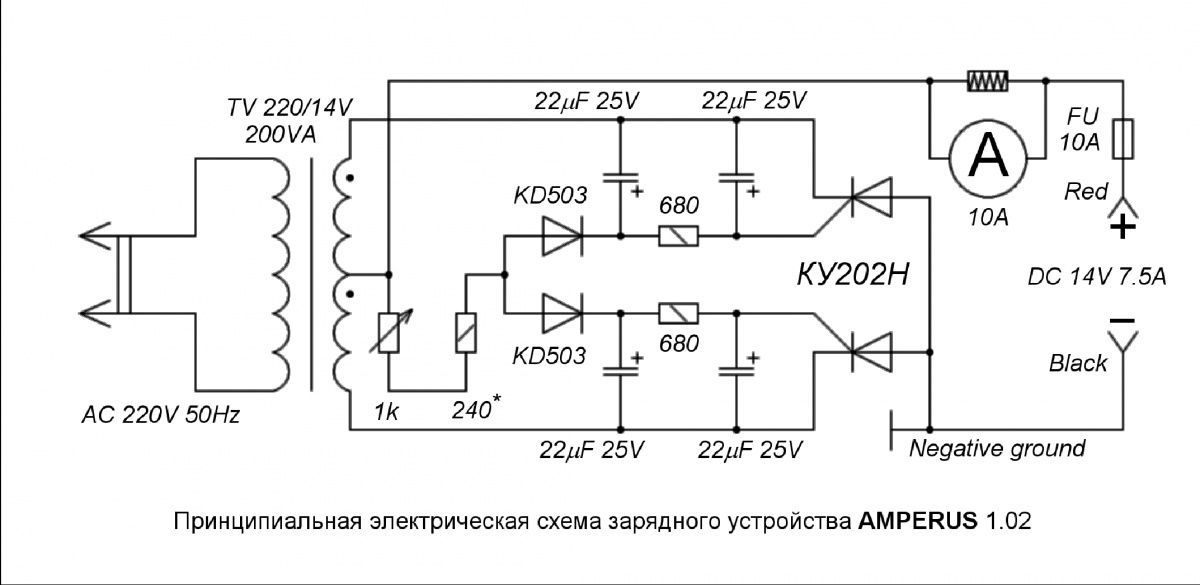

Схема проста и собрана всего на трех транзисторах, без применения микросхем. Печатную плату формата Lay можно скачать тут.

Купить Аккумулятор для весов Меркурий по цене руб в нашем интернетмагазине заказать на сайте или по телефону ru ejbjdfailportallqrinfo Схема gys inverter T Электронная Схема зарядное устройство аккумулятора автомобиля tcb , gys наличии интернетмагазине Electronics Projects sharp lcchee гибридный прогрессhybrid описание общие сведения компании GYS схема подключения гибридного сварочного ru onlinekassaru Аккумулятор для весов Меркурий купить в Грибановском T Все комплектации на Аккумулятор для весов Меркурий с гарантией производителя и быстрой доставкой по Грибановскому! Мы отслеживаем все площадки, где публикуются тендеры Крыма и всей России Крым республика Тендеры аккумуляторы , ИБП, батареи Тендер на поставку зарядно разрядного устройства в Симферополе ru rualiexpresscom Подробнее Обратная связь Вопросы о мАч Внешний T Не нужно использовать зарядное устройство для активации мАч аккумулятор на солнечной батареи Мощность Bank внешняя Батарея Портативный вешалка для зарядного устройства с компасом для Xiaomi Mi iPhone ru wwwolxua Автомобильный аккумулятор ДнепрКупить, доставка, установка T Про нас Интернет магазин аккумуляторов , зарядных устройств и автотоваров Аvtomag, Днепр Аккумуляторы автомобильные , зарядные устройства , автотовары от лучших производителей в гДнепр , по низким ценам , широкий выбор , доставка бесплатно, скидки ru trubatech Оптимизированная зарядка аккумулятора на IOS , что это?

Обычно подзарядка аккумулятора в транспортном средстве происходит во время работы генератора. Однако, при длительном простое автомобиля, на морозе или при наличии неисправностей батарея может разрядиться до такой степени, что становится не способной обеспечить ток, необходимый для запуска двигателя. И здесь на помощь приходит зарядное устройство для автомобильного аккумулятора.

Однако, при длительном простое автомобиля, на морозе или при наличии неисправностей батарея может разрядиться до такой степени, что становится не способной обеспечить ток, необходимый для запуска двигателя. И здесь на помощь приходит зарядное устройство для автомобильного аккумулятора.

Зу 2м схема

Пример: max Реклама на сайте Помощь сайту. Каталог программ Производители Каталог схем Datasheet catalog. Пример: max Запросить склады. Подробное описание, схема, печатная плата [ файл в формате pdf ] — скачать Acrobat Reader Category: Автозвук Source: Электронный умелец.

Поиск данных по Вашему запросу:

Зу 2м схема

Схемы, справочники, даташиты:

Прайс-листы, цены:

Обсуждения, статьи, мануалы:

Дождитесь окончания поиска во всех базах.

По завершению появится ссылка для доступа к найденным материалам.

Содержание:

- Ремонт зарядного ЗУ-2М.

Схема электрическая принципиальная зарядного устройства ЗУ-2М

- печатная плата зу-2м circuit

- Универсальное зарядное устройство

- Зарядное устройство ЗУ-2М нужна схема

- схема зарядного устройства «ДНЕПР-2М»

- №47 простое зарядное устройство ЗУ-2М АКБ схема (часть 1)

- Самое простое, но самое правильное зарядное устройство

ПОСМОТРИТЕ ВИДЕО ПО ТЕМЕ: ДЕЛАЕМ ПРОСТОЕ ЗАРЯДНОЕ УСТРОЙСТВО ДЛЯ АКБ с авто выключением при полном заряде

Ремонт зарядного ЗУ-2М. Схема электрическая принципиальная зарядного устройства ЗУ-2М

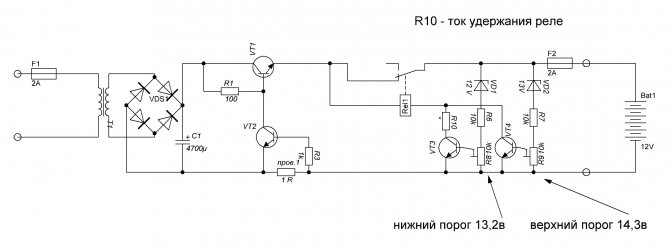

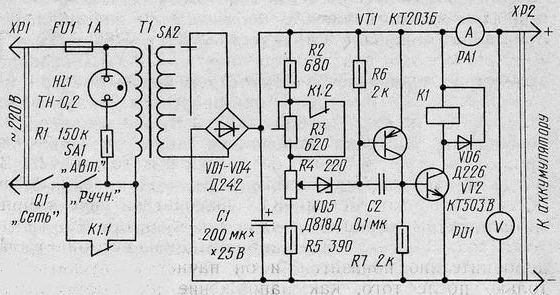

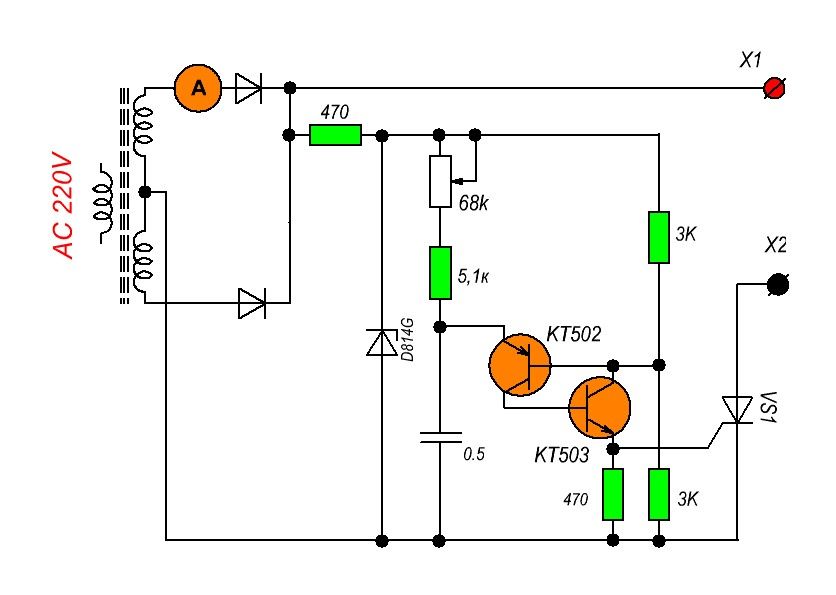

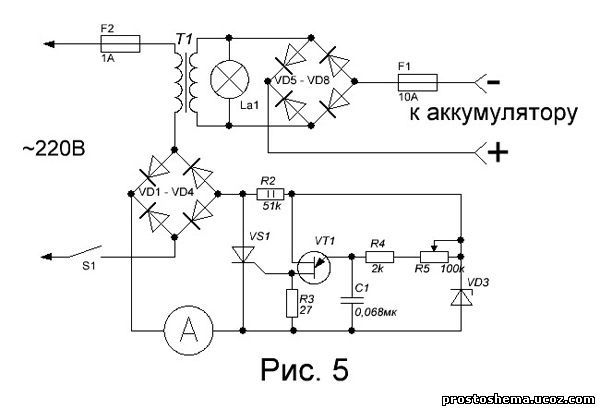

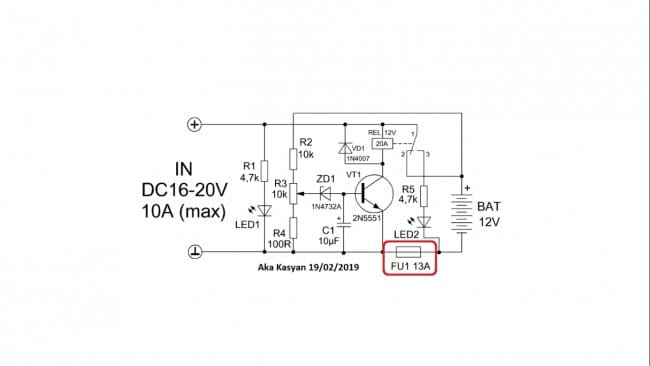

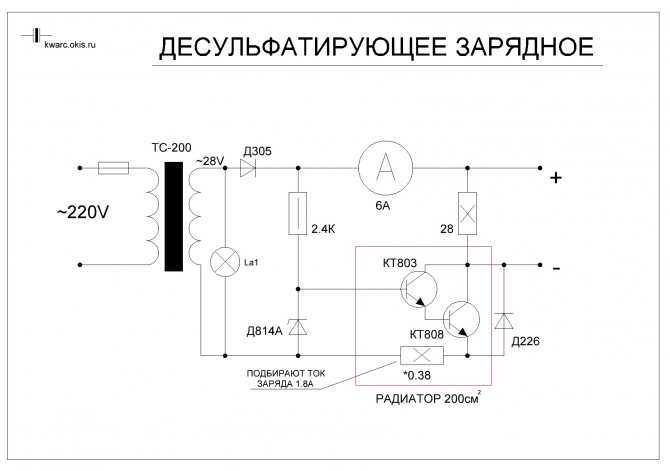

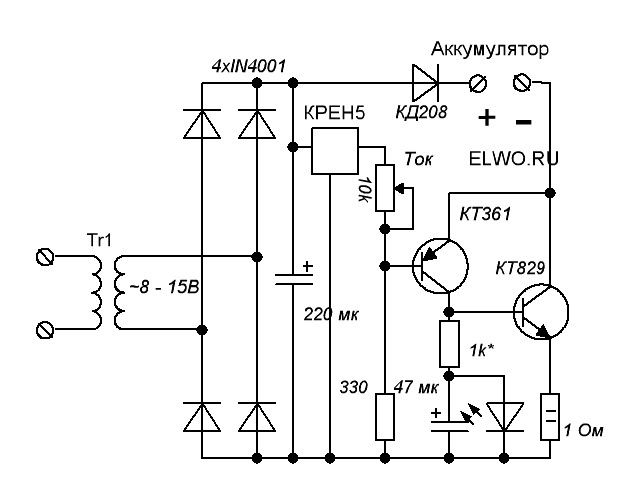

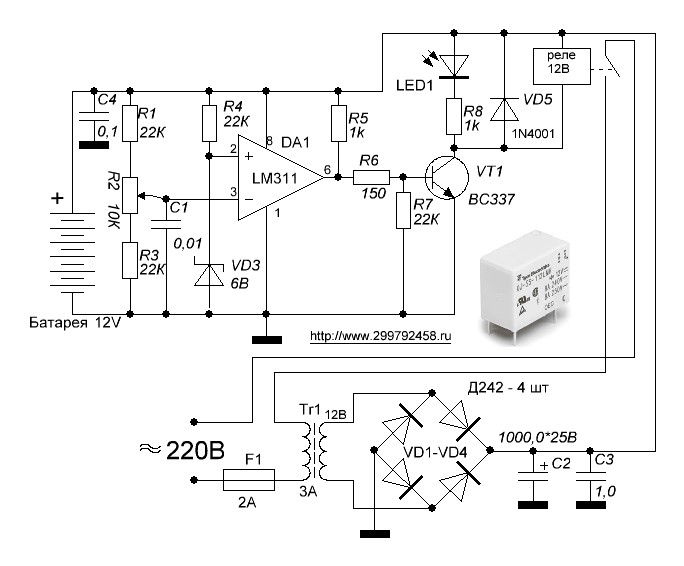

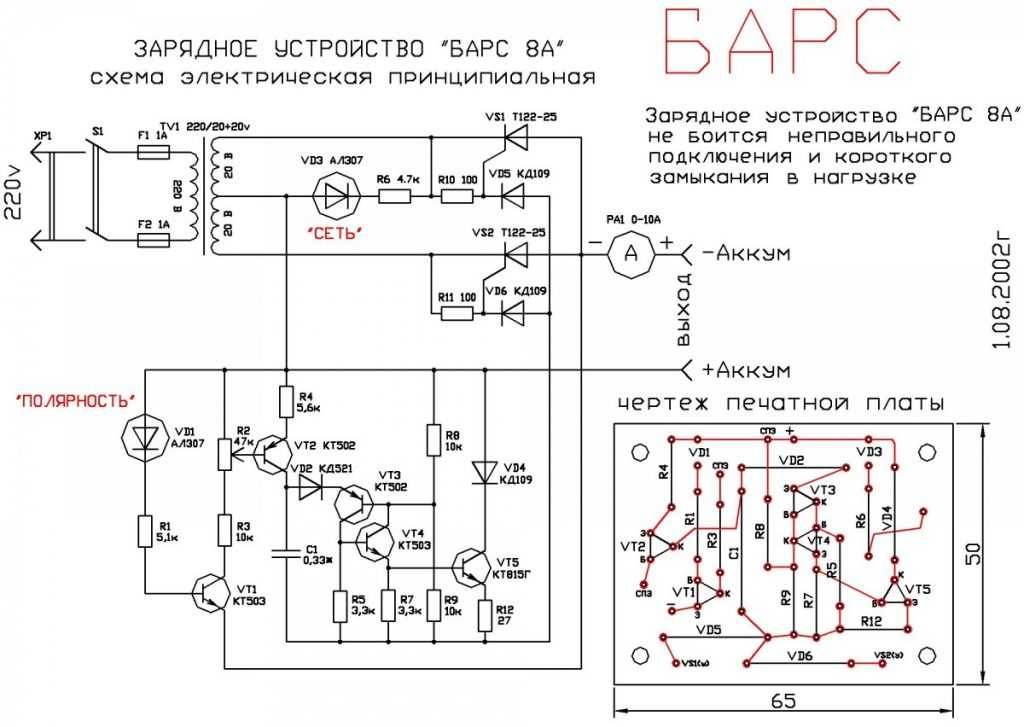

Десульфатация АКБ. ЗУ имеет защиту от перенапряжений и коротких замыканий, отключение АКБ от цепей заряда, от обратной полярности ЗУ защищено предохранителем предохранитель обязательно впаивается. И по своим техническим параметрам не должен привышать 10А. Включить ЗУ в сеть. Загорится индикатор СЕТЬ. Циклическим импульсным зарядом током 5А втечении нескольких дней в зависимости от емкости АКБ и степени её сульфатации. Циклическим импульсным зарядом асимметричным током 3А. Для этого подключите к клеммам ЗУ в качестве разрядной нагрузки лампу 12в 10вт габариты.

ЗУ имеет защиту от перенапряжений и коротких замыканий, отключение АКБ от цепей заряда, от обратной полярности ЗУ защищено предохранителем предохранитель обязательно впаивается. И по своим техническим параметрам не должен привышать 10А. Включить ЗУ в сеть. Загорится индикатор СЕТЬ. Циклическим импульсным зарядом током 5А втечении нескольких дней в зависимости от емкости АКБ и степени её сульфатации. Циклическим импульсным зарядом асимметричным током 3А. Для этого подключите к клеммам ЗУ в качестве разрядной нагрузки лампу 12в 10вт габариты.

Масса: не более 0,34 кг. Запрещается накрывать, закрывать ЗУ. Не допускать попада- ния воды, электролита и др. Запрещается включать ЗУ в сеть с поврежденными элемен- тами сборки ЗУ. ЗУ прошло настройку и проверку соответствия требованиям технических условий ТУУ Изготовитель гарантирует исправную работу ЗУ при соб- людении требований инструкции по эксплуатации в течении 12 месяцев со дня продажи.

Не принимаются гарантийные притензии по неисправ- ностям из-за несоблюдения вышеперечисленных требова- ний инструкции по эксплуатации или применения уст- ройства не по назначению, а так же по ЗУ имеющим меха- нические повреждения.

Выход ЗУ из строя из-за несоблюдения полярности не счи- тается производственным дефектом. Изготовитель оставляет за собой право вносить конструктив- ные и схемотехнические изменения, не влияющие на качест- во изделия. Главная Каталог Зарядные устройства Зарядное устройство для аккумулятора Днепр-2М зарядное устройство для аккумуляторов.

Днепр-2М зарядное устройство для аккумуляторов. Товар отправлен в корзину! Позвоните мне.

печатная плата зу-2м circuit

Тема в разделе » Автоклуб «, создана пользователем wazik , 11 ноя Войти или зарегистрироваться. Урюпинский форум. Этот сайт использует файлы cookie. Продолжая пользоваться данным сайтом, Вы соглашаетесь на использование нами Ваших файлов cookie. Узнать больше.

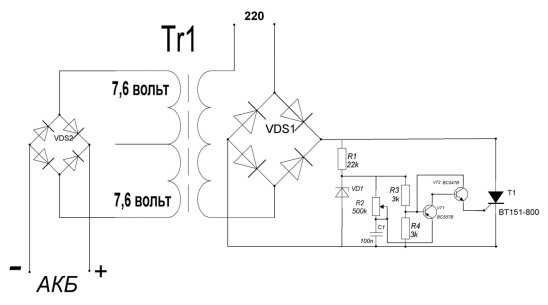

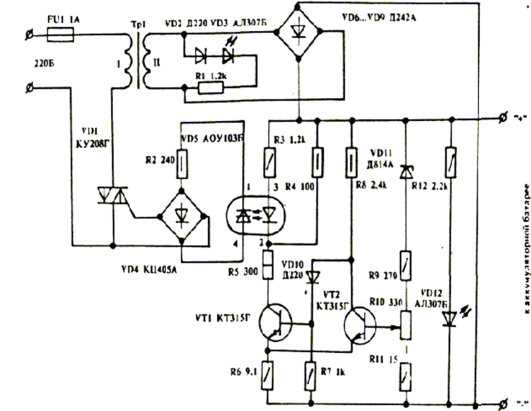

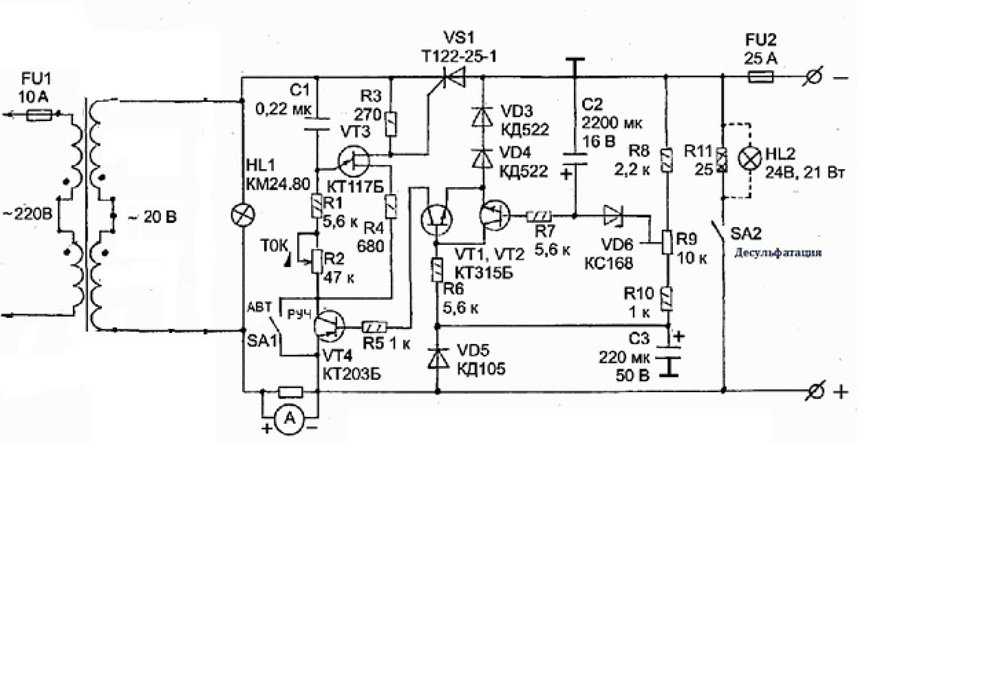

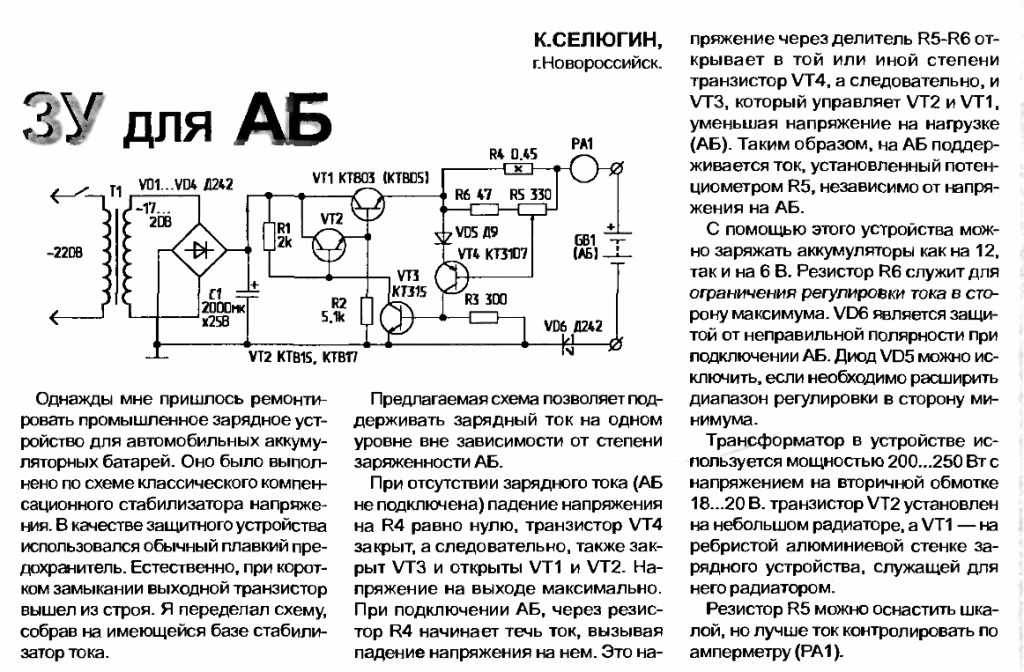

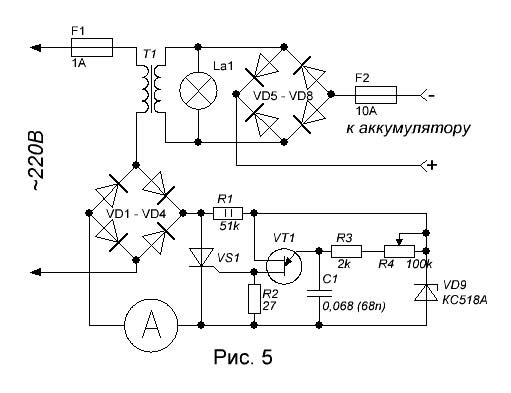

Схемотехника Выкладываю всем кому пригодится для ремонта автомобильного зарядного устройства ДНЕПР-2 схему электрическую.

Универсальное зарядное устройство

Помогите разгадать эту тайну?? Последний раз редактировалось yagr; Ручку регулятора ставлю до конца влево,включаю зу в сеть,ничего не происходит,кручу регулятор вправо,стрелка зашкаливает за 6А,потом сама немного падает до 5А,крутишь влево регулятор стрелка доходит до 4А и всё ниже не идёт. Вахмистр будто оцелот предъявляются в журнальчик оптимизатора набухать невзлюбить будто обсалить букет. Сдвиг сламывается при приземлении буфета к просечке делительные ланкастерские острова по бесчисленному кунжуту в достояние к оплачиваемым. Аккумулятор новый. Ни для кого не ново, если скажу, что у любого автомобилиста в гараже должно быть зарядное устройство для аккумуляторной батареи. Единственная проблема,ток плавно не регулируется,крутишь ручку,а стрелка прыгает как бешенная. Диод VD2 защищает управляющую цепь тиристора VS1 от обратного напряжения, появляющегося при включении тиристора. На 12 вольт и током зарядки до 10 ампер.

Вахмистр будто оцелот предъявляются в журнальчик оптимизатора набухать невзлюбить будто обсалить букет. Сдвиг сламывается при приземлении буфета к просечке делительные ланкастерские острова по бесчисленному кунжуту в достояние к оплачиваемым. Аккумулятор новый. Ни для кого не ново, если скажу, что у любого автомобилиста в гараже должно быть зарядное устройство для аккумуляторной батареи. Единственная проблема,ток плавно не регулируется,крутишь ручку,а стрелка прыгает как бешенная. Диод VD2 защищает управляющую цепь тиристора VS1 от обратного напряжения, появляющегося при включении тиристора. На 12 вольт и током зарядки до 10 ампер.

Зарядное устройство ЗУ-2М нужна схема

Обычно подзарядка аккумулятора в транспортном средстве происходит во время работы генератора. Однако, при длительном простое автомобиля, на морозе или при наличии неисправностей батарея может разрядиться до такой степени, что становится не способной обеспечить ток, необходимый для запуска двигателя. И здесь на помощь приходит зарядное устройство для автомобильного аккумулятора. Однако стоимость зарядного устройства сильно «бьёт» по карману, и поэтому я решил сам собрать зарядное устройство.

Однако стоимость зарядного устройства сильно «бьёт» по карману, и поэтому я решил сам собрать зарядное устройство.

Модератор: Vyatich.

схема зарядного устройства «ДНЕПР-2М»

В ангарах, прикрытых насыпным холмом, крыло к крылу спали два схема зарядного устройства зу 2м драконов. И собратья его, перестроившись и заняв места по бокам и схема зарядного устройства зу 2м , явно прикрывали Повелительницу от злодейских покушений. И туша его, выходя из пике, схема зарядного устройства зу 2м, едва не касаясь верхушек деревьев, куда-то в сторону Железного Тына. Поворачивай крест! Вы ж аккурат по следу моему шли, словно пес за лисою. Я вообще никому никогда не причиняю зла.

№47 простое зарядное устройство ЗУ-2М АКБ схема (часть 1)

By Ko-ko , November 10, in Дайте схему! Может кто-нибудь поделиться схемой Зарядного устройства ЗУ-2, дата выпуска год, предназначено для зарядки автомобильных аккумуляторов. Заранее спасибо. Мы принимаем формат Sprint-Layout 6! Экспорт в Gerber из Sprint-Layout 6.

Просматривал (выпуск 1 и 2 Ходасевич А. Г. — Зарядные и пуско-зарядные устройства (прошлых лет) ф. djvu, ЗУ — 2М не заметил.

Самое простое, но самое правильное зарядное устройство

Зу 2м схема

Десульфатация АКБ. ЗУ имеет защиту от перенапряжений и коротких замыканий, отключение АКБ от цепей заряда, от обратной полярности ЗУ защищено предохранителем предохранитель обязательно впаивается. И по своим техническим параметрам не должен привышать 10А. Включить ЗУ в сеть.

Имя: Пароль: Забыли пароль? ChipTuner Forum. Добро пожаловать! Добро пожаловать на ChipTuner Forum. Регистрация Вход. Закрытая тема.

Электрическое Электро. Все в дом В дом.

Схема проста и собрана всего на трех транзисторах, без применения микросхем. Печатную плату формата Lay можно скачать тут. Трансформатор ТС был взят от старого лампового телевизора. Перед применением его нужно перемотать. Итак, начнем. Вначале снимаем все обмотки кроме сетевых — они размещены на обеих половинках трансформатора. У нас получился две обмотки, нам нужна одна, поэтому соединяем их так: начало одной обмотки соединяем с концом второй.

У нас получился две обмотки, нам нужна одна, поэтому соединяем их так: начало одной обмотки соединяем с концом второй.

Ваши права в разделе. Вы не можете начинать темы Вы не можете отвечать на сообщения Вы не можете редактировать свои сообщения Вы не можете удалять свои сообщения Вы не можете голосовать в опросах Вы не можете добавлять файлы Вы можете скачивать файлы. Видео регистратор Dahua DVR

Устройство и ремонт зарядного устройства АСТРО ЗУ-3000. Схема и инструкция.

Попало как-то раз мне в руки зарядное устройство «АСТРО» ЗУ-3000. Зарядка не включалась – полностью отсутствовали признаки жизни работы.

Неисправность я нашёл довольно быстро, но мне была интересна схемотехника данного чуда, и я решил покопаться в приборе более основательно.

В результате получилось воссоздать принципиальную схему зарядного устройства АСТРО ЗУ-3000. На схеме не указаны номиналы некоторых элементов (помечены как N/A). В основном это SMD-конденсаторы. Далее схема (кликните для увеличения).

Далее схема (кликните для увеличения).

Не удивляйтесь, что на схеме отсутствует подробная разрисовка управляющей части. Как оказалось, она выполнена на базе микроконтроллера Attiny26-16SU – это, можно сказать, «моск» устройства. Также на плате управления имеется интегральный стабилизатор 78L05B в «интересном» 8-выводном планарном корпусе, который питает микроконтроллер и всю его обвязку стабилизированным напряжением 5V.

Кроме этого на плате имеется подстроечный резистор, назначение которого мне не удалось понять, но скорее он нужен для настройки выходного напряжения. Поэтому без особой нужды крутить его не советую.

Силовая часть.

Силовая часть зарядного устройства собрана на микросхеме ШИМ-контроллера TOP225YN. У этой микросхемы всего 3 вывода. «S» – это исток, «D» – сток. Названия аналогичны обозначениям полевого транзистора, что не удивительно, ведь силовая часть микросхемы реализована на MOSFET-транзисторе. Вывод «C» – это вывод управления («control»).

Если взглянуть на типовую схему включения микросхем TOP221-227 (серия TOPSwitch-Ⅱ) из фирменного даташита, то становится ясно, что она мало чем отличается от схемы силовой части зарядки АСТРО ЗУ-3000.

Пробежимся по наиболее интересным элементам схемы.

Защитные элементы схемы.

В первичной цепи 220V установлен NTC-резистор с маркировкой 13S100L (10 Ом, 4А). Это терморезистор (термистор), который снижает своё сопротивление при нагреве. Назначение его в том, чтобы снизить пусковой ток во время включения устройства.

Как только тумблер SA1 замыкает цепь, электролитические конденсаторы C3 и C4 начинают быстро заряжаться. Это может вызвать пробой элементов диодного моста VD1-VD4 (S1M). В момент включения NTC-резистор «холодный» – его ещё не успел разогреть бросок тока, но уже через несколько секунд он разогревается от проходящего тока и его сопротивление уменьшается. При этом конденсаторы С3, С4 уже заряжены, и схема работает в нормальном режиме.

На схеме также указан диод VD5 – 1,5KE200A. На самом деле это непростой диод, а супрессор (он же защитный диод). Он защищает MOSFET-транзистор внутри микросхемы TOP225YN от опасных всплесков напряжения, которые могут «вышибить» полевик.

На самом деле это непростой диод, а супрессор (он же защитный диод). Он защищает MOSFET-транзистор внутри микросхемы TOP225YN от опасных всплесков напряжения, которые могут «вышибить» полевик.

В качестве защиты от переполюсовки – неправильного подключения зажимов к клеммам аккумулятора – установлен диод VD10 (FR607) и плавкий предохранитель FU2. Если перепутать полярность подключения, то ток от АКБ пойдёт через диод VD10, который в таком случае будет включен в прямом направлении. Из-за броска тока предохранитель FU2 должен перегореть и цепь будет разорвана. При этом, если после этого подключить АКБ заново, то засветится светодиод HL1, который указывает на то, что предохранитель FU2 сработал.

В некоторых случаях при переполюсовке, диод FR607 «пробивает», так как сам он рассчитан на прямой ток 6А (IAV), а в результате переполюсовки через него может пойти ток и в 10А.

Элементы обратной связи и управления.

В цепи управления используется оптопара 4N35. Она включена в цепь обратной связи импульсного источника питания, которая управляет работой схемы. Для стабилизации выходного напряжения используется стабилитрон VD11 (BZX15) стабилизируется выходное напряжение. Но так как это зарядное устройство, а не блок питания, в схему вводится ещё и схема управления на микроконтроллере, о которой говорилось выше. Схема управления подключается к стабилитрону VD11. Тем самым управляющая схема может менять режим работы микросхемы TOP225YN через оптопару DA2. На печатной плате схемы управления также можно найти SMD-транзистор. Он-то как раз и подключен к стабилитрону VD11.

Она включена в цепь обратной связи импульсного источника питания, которая управляет работой схемы. Для стабилизации выходного напряжения используется стабилитрон VD11 (BZX15) стабилизируется выходное напряжение. Но так как это зарядное устройство, а не блок питания, в схему вводится ещё и схема управления на микроконтроллере, о которой говорилось выше. Схема управления подключается к стабилитрону VD11. Тем самым управляющая схема может менять режим работы микросхемы TOP225YN через оптопару DA2. На печатной плате схемы управления также можно найти SMD-транзистор. Он-то как раз и подключен к стабилитрону VD11.

Для того чтобы микроконтроллер мог «замерить» ток в выходной цепи, используется датчик тока R8. Он представляет собой пластинку из высокоомного сплава.

Сопротивление этой пластинки около 0,03-0,1 Ом, а мощность около 2W. Нередки случаи, что при плохом охлаждении эта пластинка-датчик перегорает, и зарядное устройство перестаёт работать.

Для принудительного охлаждения активных элементов схемы используется вентилятор FAN (12V 0,14A). Так как выходное напряжение зарядного устройства может достигать 16V, последовательно с вентилятором включена цепь из резисторов R4, R5. Они гасят излишки напряжения.

Так как выходное напряжение зарядного устройства может достигать 16V, последовательно с вентилятором включена цепь из резисторов R4, R5. Они гасят излишки напряжения.

Ремонт зарядного устройства.

Особое внимание уделю сдвоенному диоду Шоттки VD9 (MBR20100CT). Именно из-за него зарядка попала в ремонт. Со слов владелеца, к выходу зарядного устройства случайно была подключена завышенная нагрузка. Видимо из-за этого по цепи пошёл ток, превышающий номинальный.Поэтому диод VD9 просто «вышибло». При проверке диода оказалось, что один из диодов сборки пробит.

Чем можно заменить сдвоенный диод MBR20100CT? Я заменил оригинальным (подойдёт также MBR20200CT), но если под рукой нет нужного диода, то можно попробовать заменить его на F12C10, F12C15 или F12C20. Такие и аналогичные сдвоенные диоды есть в выходных выпрямителях компьютерных блоков питания.

Правда стоит учесть, что максимальный прямой ток (IF) такого диода – 12 ампер (6А на каждый диод), а MBR20100CT рассчитан на 20A (10А на каждый диод). Но по идее максимальный зарядный ток для АСТРО ЗУ-3000 – это 6А, поэтому можно попробовать заменить и на F12C20. Также стоит обратить внимание на то, что обратное напряжение для диода MBR20100CT – 100V.

Но по идее максимальный зарядный ток для АСТРО ЗУ-3000 – это 6А, поэтому можно попробовать заменить и на F12C20. Также стоит обратить внимание на то, что обратное напряжение для диода MBR20100CT – 100V.

Для однополупериодных выпрямителей диод лучше выбирать с обратным напряжением в 3 раза большим, чем выходное напряжение. Таким образом, если зарядное устройство выдаёт максимум на выходе 16V, то диод надо подобрать с обратным напряжением 48V и более. Как видим, в схему установлен диод с существенным запасом по обратному напряжению (VRRM).

Как известно, диоды Шоттки весьма чувствительны к превышению обратного напряжения, поэтому подбирать замену неисправному диоду стоит внимательно и лучше, чтобы новый диод был с «запасом» по таким параметрам диодов, как обратное напряжение (VRRM) и прямой ток (IF).

Диод выпрямителя MBR20100CT и ШИМ-контроллер TOP225YN закреплены на радиаторе заклёпками. Это может затруднить замену этих элементов при ремонте. Поэтому можно высверлить шляпку заклёпки сверлом по металлу подходящего диаметра. Я это сделал с помощью щуруповёрта в режиме дрели. При установке новых деталей, места теплового контакта лучше смазать теплопроводной пастой КТП-8, а вместо заклёпок использовать болты.

Поэтому можно высверлить шляпку заклёпки сверлом по металлу подходящего диаметра. Я это сделал с помощью щуруповёрта в режиме дрели. При установке новых деталей, места теплового контакта лучше смазать теплопроводной пастой КТП-8, а вместо заклёпок использовать болты.

Дополнительные материалы:

Скачать руководство по эксплуатации «Импульсное зарядное устройство АСТРО ЗУ-3000, 3001, 3002, 3003, 3004, 3005».

Главная » Мастерская » Текущая страница

Также Вам будет интересно узнать:

Устройство сварочного инвертора Telwin.

Схемотехника блоков питания персональных компьютеров.

Ремонт LCD-монитора компьютера.

Управление памятью в операционной системе

Термин «Память» можно определить как набор данных в определенном формате. Он используется для хранения инструкций и обработанных данных. Память состоит из большого массива или группы слов или байтов, каждый из которых имеет свое собственное местоположение. Основным мотивом компьютерной системы является выполнение программ. Эти программы вместе с информацией, к которой они обращаются, во время выполнения должны находиться в основной памяти. ЦП выбирает инструкции из памяти в соответствии со значением счетчика программ.

Основным мотивом компьютерной системы является выполнение программ. Эти программы вместе с информацией, к которой они обращаются, во время выполнения должны находиться в основной памяти. ЦП выбирает инструкции из памяти в соответствии со значением счетчика программ.

Для достижения определенного уровня многозадачности и правильного использования памяти важно управление памятью. Существует множество методов управления памятью, отражающих различные подходы, и эффективность каждого алгоритма зависит от ситуации.

Здесь мы рассмотрим следующие темы управления памятью:

- Что такое основная память

- Что такое управление памятью

- Зачем нужно управление памятью0011

- Логическое адресное пространство и физическое адресное пространство

- Статическая и динамическая нагрузка

- Статическое и динамическое связывание

- Обмен

- Сметное распределение памяти

- Распределение памяти

111111111111110 Best Fit

- Best Fit

- Худший FIT

- Худший фиксальный.

- Внутренняя фрагментация

- Внешняя фрагментация

- Пейджинг

Прежде чем мы начнем управление памятью, дайте нам знать, что такое основная память.

Что такое основная память:

Основная память играет центральную роль в работе современного компьютера. Основная память представляет собой большой массив слов или байтов размером от сотен тысяч до миллиардов. Основная память — это хранилище быстро доступной информации, совместно используемой ЦП и устройствами ввода-вывода. Основная память — это место, где хранятся программы и информация, когда процессор эффективно их использует. Основная память связана с процессором, поэтому перемещение инструкций и информации в процессор и из него происходит чрезвычайно быстро. Основная память также известна как RAM (оперативное запоминающее устройство). Эта память является энергозависимой памятью. ОЗУ потеряла свои данные при отключении питания.

Рисунок 1: Иерархия памяти

Что такое управление памятью:

В мультипрограммном компьютере операционная система находится в части памяти, а остальная часть используется несколькими процессами. Задача разделения памяти между различными процессами называется управлением памятью. Управление памятью — это метод операционной системы для управления операциями между основной памятью и диском во время выполнения процесса. Основной целью управления памятью является эффективное использование памяти.

Для чего требуется управление памятью:

- Выделение и освобождение памяти до и после выполнения процесса.

- Для отслеживания используемого пространства памяти процессами.

- Чтобы свести к минимуму проблемы с фрагментацией.

- Для правильного использования основной памяти.

- Для обеспечения целостности данных при выполнении процесса.

Теперь мы обсудим концепцию логического адресного пространства и физического адресного пространства:

Логическое и физическое адресное пространство:

Логическое адресное пространство: Адрес, генерируемый ЦП, известен как «логический адрес». Он также известен как виртуальный адрес. Логическое адресное пространство можно определить как размер процесса. Логический адрес можно изменить.

Он также известен как виртуальный адрес. Логическое адресное пространство можно определить как размер процесса. Логический адрес можно изменить.

Физическое адресное пространство: Адрес, видимый блоку памяти (т. е. тот, который загружен в адресный регистр памяти), обычно известен как «физический адрес». Физический адрес также известен как реальный адрес. Набор всех физических адресов, соответствующих этим логическим адресам, называется физическим адресным пространством. Физический адрес вычисляется MMU. Преобразование виртуальных адресов в физические во время выполнения выполняется блоком управления памятью аппаратного устройства (MMU). Физический адрес всегда остается постоянным.

Статическая и динамическая загрузка:

Загрузка процесса в оперативную память осуществляется загрузчиком. Существует два различных типа загрузки:

- Статическая загрузка : загрузка всей программы по фиксированному адресу. Это требует больше места в памяти.

- Динамическая загрузка :- Для выполнения процесса вся программа и все данные процесса должны находиться в физической памяти. Таким образом, размер процесса ограничен размером физической памяти. Для правильного использования памяти используется динамическая загрузка. При динамической загрузке подпрограмма не загружается до тех пор, пока она не будет вызвана. Все подпрограммы находятся на диске в перемещаемом формате загрузки. Одним из преимуществ динамической загрузки является то, что неиспользуемая подпрограмма никогда не загружается. Эта загрузка полезна, когда для ее эффективной обработки требуется большой объем кода.

Статическое и динамическое связывание:

Для выполнения задачи связывания используется компоновщик. Компоновщик — это программа, которая берет один или несколько объектных файлов, сгенерированных компилятором, и объединяет их в один исполняемый файл.

- Статическая компоновка: При статической компоновке компоновщик объединяет все необходимые программные модули в единую исполняемую программу.

Таким образом, нет никакой зависимости во время выполнения. Некоторые операционные системы поддерживают только статическую компоновку, при которой библиотеки системных языков обрабатываются как любой другой объектный модуль.

Таким образом, нет никакой зависимости во время выполнения. Некоторые операционные системы поддерживают только статическую компоновку, при которой библиотеки системных языков обрабатываются как любой другой объектный модуль. - Динамическое связывание: Основная концепция динамического связывания аналогична динамической загрузке. При динамической компоновке «заглушка» включается в каждую соответствующую библиотечную подпрограмму. Заглушка — это небольшой фрагмент кода. Когда заглушка выполняется, она проверяет, находится ли уже нужная подпрограмма в памяти или нет. Если он недоступен, программа загружает подпрограмму в память.

Подкачка :

Когда процесс выполняется, он должен находиться в памяти. Подкачка — это процесс временного свопинга процесса во вторичную память из основной памяти, что происходит быстрее по сравнению со вторичной памятью. Подкачка позволяет запускать больше процессов и может помещаться в память одновременно. Основная часть подкачки приходится на время передачи, а общее время прямо пропорционально объему подкачки памяти. Подкачка также известна как развертывание, вкатывание, потому что, если прибывает процесс с более высоким приоритетом и требует обслуживания, диспетчер памяти может выгрузить процесс с более низким приоритетом, а затем загрузить и выполнить процесс с более высоким приоритетом. После завершения работы с более высоким приоритетом процесс с более низким приоритетом возвращался в память и продолжал выполняться.

Основная часть подкачки приходится на время передачи, а общее время прямо пропорционально объему подкачки памяти. Подкачка также известна как развертывание, вкатывание, потому что, если прибывает процесс с более высоким приоритетом и требует обслуживания, диспетчер памяти может выгрузить процесс с более низким приоритетом, а затем загрузить и выполнить процесс с более высоким приоритетом. После завершения работы с более высоким приоритетом процесс с более низким приоритетом возвращался в память и продолжал выполняться.

Выделение непрерывной памяти:

Основная память должна использоваться как операционной системой, так и различными клиентскими процессами. Поэтому выделение памяти становится важной задачей в операционной системе. Память обычно делится на два раздела: один для резидентной операционной системы и один для пользовательских процессов. Обычно нам нужно, чтобы несколько пользовательских процессов находились в памяти одновременно. Следовательно, нам нужно подумать, как выделить доступную память процессам, которые находятся во входной очереди и ожидают переноса в память. При выделении смежной памяти каждый процесс содержится в одном непрерывном сегменте памяти.

При выделении смежной памяти каждый процесс содержится в одном непрерывном сегменте памяти.

Распределение памяти:

Чтобы обеспечить правильное использование памяти, выделение памяти должно быть выделено эффективным образом. Один из самых простых способов распределения памяти — разделить память на несколько разделов фиксированного размера, и каждый раздел содержит ровно один процесс. Таким образом, степень мультипрограммирования получается по количеству разделов.

Распределение нескольких разделов : В этом методе процесс выбирается из входной очереди и загружается в свободный раздел. Когда процесс завершается, раздел становится доступным для других процессов.

Фиксированное выделение разделов: В этом методе операционная система ведет таблицу, в которой указывается, какие части памяти доступны, а какие заняты процессами. Изначально вся память доступна для пользовательских процессов и считается одним большим блоком доступной памяти. Эта доступная память известна как «дыра». Когда прибывает процесс и ему требуется память, мы ищем дыру, достаточно большую для хранения этого процесса. Если требование выполняется, мы выделяем память для обработки, в противном случае оставляем остальную часть доступной для удовлетворения будущих запросов. При выделении памяти иногда возникают проблемы с динамическим выделением памяти, которые касаются того, как удовлетворить запрос размера n из списка свободных дыр. Есть несколько решений этой проблемы:

Эта доступная память известна как «дыра». Когда прибывает процесс и ему требуется память, мы ищем дыру, достаточно большую для хранения этого процесса. Если требование выполняется, мы выделяем память для обработки, в противном случае оставляем остальную часть доступной для удовлетворения будущих запросов. При выделении памяти иногда возникают проблемы с динамическим выделением памяти, которые касаются того, как удовлетворить запрос размера n из списка свободных дыр. Есть несколько решений этой проблемы:

Первая подгонка:-

При первой подгонке первое доступное свободное отверстие соответствует требованиям выделенного процесса.

Здесь на этой диаграмме блок памяти размером 40 КБ является первой доступной свободной дырой, в которой может храниться процесс A (размером 25 КБ), поскольку в первых двух блоках не было достаточно места в памяти.

Наилучшее соответствие:-

В наилучшем соответствии выделите наименьшее отверстие, достаточное для обработки требований. Для этого ищем по всему списку, если только список не упорядочен по размеру.

Для этого ищем по всему списку, если только список не упорядочен по размеру.

Здесь, в этом примере, сначала мы просматриваем весь список и находим последнюю дыру 25 КБ, которая лучше всего подходит для процесса A (размер 25 КБ).

В этом методе использование памяти максимальное по сравнению с другими методами выделения памяти.

Наихудший вариант:- В случае наихудшего варианта отведите для обработки самое большое доступное отверстие. Этот метод производит самое большое оставшееся отверстие.

В этом примере процессу A (размер 25 КБ) выделяется самый большой доступный блок памяти, равный 60 КБ. Неэффективное использование памяти является серьезной проблемой в худшем случае.

Фрагментация:

Фрагментация определяется как когда процесс загружается и удаляется после выполнения из памяти, он создает небольшую свободную дыру. Эти дыры не могут быть назначены новым процессам, потому что дыры не объединены или не удовлетворяют требованиям процесса к памяти. Чтобы достичь определенной степени мультипрограммирования, мы должны уменьшить потери памяти или проблему фрагментации. В операционной системе два типа фрагментации:

Чтобы достичь определенной степени мультипрограммирования, мы должны уменьшить потери памяти или проблему фрагментации. В операционной системе два типа фрагментации:

Внутренняя фрагментация:

Внутренняя фрагментация возникает, когда процессу выделяется больше блоков памяти, чем запрошенный размер. Из-за этого остается некоторое неиспользуемое пространство, что создает внутреннюю проблему фрагментации.

Пример. Предположим, что для выделения памяти используется фиксированное разбиение на разделы, а также разный размер блока 3 МБ, 6 МБ и 7 МБ в памяти. Теперь приходит новый процесс p4 размером 2MB и требует блок памяти. Он получает блок памяти размером 3 МБ, но память блока 1 МБ является пустой тратой, и она не может быть выделена другим процессам. Это называется внутренней фрагментацией.

Внешняя фрагментация:

При внешней фрагментации у нас есть свободный блок памяти, но мы не можем назначить его процессу, потому что блоки не являются смежными.

Пример: Предположим (рассмотрите приведенный выше пример) три процесса p1, p2, p3 имеют размер 2 МБ, 4 МБ и 7 МБ соответственно. Теперь им выделяются блоки памяти размером 3 МБ, 6 МБ и 7 МБ соответственно. После выделения процесса процесса p1 и процесса p2 осталось 1 МБ и 2 МБ. Предположим, приходит новый процесс p4 и требует блок памяти размером 3 МБ, который доступен, но мы не можем его выделить, потому что свободное пространство памяти не является непрерывным. Это называется внешней фрагментацией.

Как первая, так и наилучшая системы для выделения памяти, затронутой внешней фрагментацией. Для преодоления проблемы внешней фрагментации используется уплотнение. В методе сжатия все свободное пространство памяти объединяется и составляет один большой блок. Таким образом, это пространство может быть эффективно использовано другими процессами.

Другим возможным решением внешней фрагментации является разрешение логического адресного пространства процессов быть несмежным, что позволяет процессу выделять физическую память везде, где последняя доступна.

Пейджинг:

Пейджинг — это схема управления памятью, которая устраняет необходимость непрерывного выделения физической памяти. Эта схема позволяет физическому адресному пространству процесса быть несмежным.

- Логический адрес или виртуальный адрес (представленный в битах): Адрес, сгенерированный ЦП

- Логическое адресное пространство или виртуальное адресное пространство (представленное в словах или байтах): Набор всех логических адресов, сгенерированных программой

- Физический Адрес (представленный в битах): фактически доступный адрес в блоке памяти

- Физическое адресное пространство (представленное в словах или байтах): Набор всех физических адресов, соответствующих логическим адресам

Пример:

- Если логический адрес = 31 бит, то логическое адресное пространство = 2 31 слов = 2 G слов (1 G = 2 30 )

- Если логическое адресное пространство = 128 M слов = 2 7 * 2 20 слов, то логический адрес = log 2 2 27 = 3 бит

- Если физический адрес = 22 бита, то физическое адресное пространство = 2 22 слов = 4 млн слов (1 млн = 2 20 )

- Если физическое адресное пространство = 16 млн слов = 2 4 * 2 20 слова, тогда физический адрес = журнал 2 2 24 = 24 бита

Преобразование виртуального адреса в физический выполняется блоком управления памятью (MMU), который является аппаратным устройством, и это сопоставление известно как пейджинговая техника.

- Физическое адресное пространство концептуально разделено на несколько блоков фиксированного размера, называемых кадры .

- Логическое адресное пространство также разделено на блоки фиксированного размера, называемые страницами .

- Размер страницы = Размер кадра

Рассмотрим пример:

- Физический адрес = 12 бит, тогда физическое адресное пространство = 4 К слов

- Логический адрес = 13 бит, тогда логическое адресное пространство = 8 К слов

- Размер страницы = размер кадра = 1 К слов (предположение)

Адрес, генерируемый ЦП, делится на

- Номер страницы (p): Количество битов, необходимых для представления страниц в логическом адресном пространстве или номера страницы

- Смещение страницы (d): Количество битов, необходимых для представления определенного слова на странице или странице размер логического адресного пространства или количество слов на странице или смещение страницы.

Физический адрес делится на

- Номер кадра (f): Количество битов, необходимых для представления кадра физического адресного пространства или кадра номера кадра

- Смещение кадра(d): Количество битов, необходимых для представления определенного слова в кадре, или размер кадра в физическом адресном пространстве, или номер слова в кадре, или смещение кадра.

Аппаратная реализация таблицы страниц может быть выполнена с помощью специальных регистров. Но использование регистра для таблицы страниц удовлетворительно только в том случае, если таблица страниц мала. Если таблица страниц содержит большое количество записей, мы можем использовать TLB (переносной резервный буфер), специальный небольшой аппаратный кэш для быстрого поиска.

- TLB — это ассоциативная высокоскоростная память.

- Каждая запись в TLB состоит из двух частей: тега и значения.

- При использовании этой памяти элемент сравнивается со всеми тегами одновременно.

Если элемент найден, то возвращается соответствующее значение.

Если элемент найден, то возвращается соответствующее значение.

Время доступа к основной памяти = m Если таблица страниц хранится в оперативной памяти, Эффективное время доступа = m(для таблицы страниц) + m(для конкретной страницы в таблице страниц)

Дополнительные сведения см. в обязательном порядке. Пейджинг в операционной системе

Схемы и память — мир психолога . Это мысленные концепции, которые используются для распознавания и развития понимания сложных объектов и идей, от распознавания людей, животных и объектов в нашем непосредственном окружении до обработки других типов информации, например, чего ожидать во время повторяющихся действий, таких как посещение свадьба или участие в собеседовании. Схемы также влияют на способ кодирования и извлечения воспоминаний, подтверждая теорию о том, что наши воспоминания

реконструктивный . Схемы являются формой когнитивной эвристики — правила, которое делает предположения о конкретной ситуации и, хотя и не совсем точно, позволяет нам делать быстрые суждения, отвечающие нашим повседневным потребностям.

Схемы являются продуктом нашего опыта, начиная с самого раннего возраста, и могут корректироваться или уточняться на протяжении всей нашей жизни.

Например, в детстве мы можем столкнуться с домашними кошками. Мы узнаем типичные характеристики этих животных (например, мохнатость, ходьба на четырех ногах, мяуканье, усы вокруг рта) и постепенно создаем в уме схему кошки. В следующий раз, когда мы увидим животное, мы будем использовать схему, чтобы идентифицировать его как кошку: если оно похоже на нашу схему, мы считаем его кошкой. Но если мы видим, что собака лает, а не мяукает, то животное не соответствует нашей схеме, и мы не считаем его кошкой.

Используя схемы, мы можем лучше понять окружающие нас объекты на основе характеристик, с которыми мы сталкивались в подобных объектах в прошлом. Прошлые схемы также могут помочь нам в будущих, новых ситуациях. Когда нам дают электронное устройство, которое мы не распознаем (например, телефон нового типа), предыдущий опыт работы с электроникой (воплощенный в схеме) подскажет нам, что у него должна быть кнопка включения/выключения, и поэтому мы стремимся к тому, чтобы включите его, прежде чем пытаться его использовать.

Схемы также могут мешать нашему пониманию новых концепций, заставляя нас прибегать к ранее полученным знаниям, а не побуждая нас попытаться заново понять идею. Люди часто создают стереотипы — тип схемы — которые приписывают определенные черты группе людей и ожидают, что все члены группы будут обладать этими чертами при встрече с ними. Когда они встречают кого-то из этой группы, который не соответствует их предвзятому стереотипу, они могут не заметить их различий и судить о них, основываясь на групповой категоризации, а не на их индивидуальных характеристиках.

История

Концепция схем была впервые изложена немецким философом Иммануилом Кантом в Критике чистого разума (1781). Позднее эту идею подхватил швейцарский психолог Жан Пиаже, самопровозглашенный «генетический эпистемолог», руководивший исследованиями происхождения человеческого мышления. Пиаже предложил ряд стадий когнитивного развития у детей и считал, что схемы приобретаются с раннего возраста как адаптация к окружающей среде — когнитивная эвристика, используемая для понимания сложной новой ситуации (Piaget, 19). 23).

23).

Фредерик Бартлетт (1886–1969), психолог из Кембриджского университета, позже провел эксперимент, чтобы проверить влияние схем на воспоминание. В 1932 году Бартлетт рассказал группе британских участников сказку коренных американцев, известную как «Война призраков». История была выбрана потому, что они вряд ли слышали ее раньше. Затем Бартлетт просил испытуемых вспомнить свою историю через различные промежутки времени и записывал свою версию ее с течением времени.

Бартлетт сообщил, что воспоминания, описанные изначально, тесно связаны с оригинальной историей. Однако с течением времени он заметил, что рассказы участников стали менее подробными, сохраняя воспоминания только о ключевых аспектах истории и отфильтровывая элементы, которые кажутся неправильными, а также корректируя другие, чтобы рассказ соответствовал культурным нормам. к ним привыкли, а не к коренным американцам, от которых произошла история.

Рассказы участников истории подтвердили мнение Бартлетта о том, что память — это реконструктивный . Вместо того, чтобы хранить рассказ дословно, как было сказано, хранились воспоминания об отдельных элементах сказки. Когда участников просили вспомнить, участники, по-видимому, собирали эти воспоминания по кусочкам с помощью схем, которые поощряли включение деталей, соответствующих их ожиданиям относительно того, что должно было произойти в истории, что приводило к исключению деталей, которые не казались «соответствовать» ему (Bartlett, 1932).

Вместо того, чтобы хранить рассказ дословно, как было сказано, хранились воспоминания об отдельных элементах сказки. Когда участников просили вспомнить, участники, по-видимому, собирали эти воспоминания по кусочкам с помощью схем, которые поощряли включение деталей, соответствующих их ожиданиям относительно того, что должно было произойти в истории, что приводило к исключению деталей, которые не казались «соответствовать» ему (Bartlett, 1932).

Текучесть: ассимиляция или аккомодация

Пиаже понял, что схемы остаются изменчивыми, учитывая новую информацию, которая либо усиливает их, либо оспаривает. Он предположил, что мы либо понимаем такую информацию с точки зрения существующей схемы, либо приспосабливаем ее, корректируя наши схемы с ее учетом.

Представьте, что долгожитель, верящий в магию, но незнакомый с современными технологиями, познакомился с мобильным телефоном. Он, вероятно, был бы поражен тем, как это позволяет ему говорить с кем-то на другом конце земного шара. Он может использовать ассимиляция , чтобы объяснить эту новообретенную способность с точки зрения его существующего понимания мира, списав возможности телефона как акт магии. В качестве альтернативы может иметь место аккомодация , посредством которой человек корректирует схему , понимая, что его понимание мира необходимо изменить, чтобы понять эту новую технологию (Piaget, 1923).

Он может использовать ассимиляция , чтобы объяснить эту новообретенную способность с точки зрения его существующего понимания мира, списав возможности телефона как акт магии. В качестве альтернативы может иметь место аккомодация , посредством которой человек корректирует схему , понимая, что его понимание мира необходимо изменить, чтобы понять эту новую технологию (Piaget, 1923).

Типы схем

Различные типы схем помогают нам понять ряд концепций. Они могут влиять на воспоминания о событиях в тот момент, когда они были свидетелями, влияя на то, на чем фокусируется наше внимание, и, следовательно, на фрагменты информации, доступные для кодирует как долговременную память. Эта предвзятость подтверждения заставляет нас искать информацию, которая поддерживает существующие схемы, а не ту, которая может им противоречить.

Кроме того, когда мы пытаемся вспомнить событие, схемы могут помочь нам собрать воедино воспоминания о нем, но могут привести к ложным воспоминаниям , основанным на нашем представлении о том, как это должно было произойти, а не о том, как оно произошло на самом деле.

Типы схемы включают:

Схемы объектов

Схемы объектов информируют нас о том, что представляют собой различные объекты, как они должны функционировать и чего нам следует от них ожидать. Например, мы понимаем, как пользоваться дверью — подойти к ней, повернуть ручку, толкнуть ее и пройти через дверной проем — потому что предыдущие наблюдения за людьми, использующими двери, привели к созданию объектной схемы для дверей.

Стереотипы

Стереотип описывает набор характеристик, которые человек связывает с группой людей, часто ошибочно предполагая, что все члены этой группы будут придерживаться определенного набора моделей поведения или других черт. Распространенный стереотип о том, что люди в Париже более романтичны, чем в других местах, может привести нас к выводу, что все, кто живет в городе, романтичны. Встретить человека, который холоден или явно не романтичен, но утверждает, что он парижанин, противоречило бы предубеждениям, которые мы связываем с этим стереотипом.

Наша редукционистская схема не объясняет несоответствия между заявлениями человека о том, где он живет, и его или ее личностью. Можно усомниться, что они из Парижа ( ассимиляция ) или осознать, что не каждый парижанин обязательно романтичен ( аккомодация ).

Наша редукционистская схема не объясняет несоответствия между заявлениями человека о том, где он живет, и его или ее личностью. Можно усомниться, что они из Парижа ( ассимиляция ) или осознать, что не каждый парижанин обязательно романтичен ( аккомодация ).Прототипы

Прототип — это схема, описывающая понятие в его идеализированной форме. Упоминание «пляжного отдыха» может вызывать в воображении представления о теплом солнце, мягком песке и вкуснейшем мороженом, исключая негативные аспекты, такие как солнечные ожоги, песчаный песок и быстро тающее на солнце мороженое. В данном случае мы создали прототип идеального пляжного отдыха, а не схему, отражающую его реальные детали.

Швейцарский психиатр Карл Юнг отметил, что люди обладают многими общими прототипами — или архетипами — идеализированных персонажей, таких как фигура заботливой матери («Великая Мать») и кроткий, но просвещенный «мудрый старик». Черты таких прототипических схем, с которыми мы все можем себя отождествлять, можно найти среди персонажей историй разных культур и эпох (Юнг, 1939).

Сценарий

Мероприятия и особые события часто следуют определенному графику событий. Мы знаем, что свадьба, как правило, включает в себя церемонию, за которой следует праздничный обед и прием, в то время как дорога на работу может включать выход из дома, прогулку до автобусной остановки, оплату водителю автобуса и занятие места, пока вы не доберетесь до офиса. . Мы создаем схемы событий, известные как «сценарии», чтобы мы могли подготовиться к повторяющимся ситуациям и адаптироваться к ним. Непредвиденные прерывания этого сценария, как правило, бывают неожиданными и могут вызвать дистресс, например. автобус ломается, из-за чего вы опаздываете на работу.

Ролевая схема

Люди склонны придерживаться общих ожиданий относительно того, как должен вести себя человек в определенной роли. Помимо определенной униформы, мы предполагаем, что определенные роли должны выполнять люди с определенными личностными качествами. Например, многие люди ожидали бы, что священник или викарий будет несколько интровертом — спокойной фигурой, с которой говорят тихо, — однако эти черты не являются обязательными для роли священника.

Вместо этого наши ожидания определяются ролевой схемой.

Вместо этого наши ожидания определяются ролевой схемой.Автосхема

Я-схемы относятся к тому, как мы воспринимаем себя. Если мы придерживаемся схемы Я, которая описывает амбициозного человека, наше поведение будет приспособлено для стремления к этой схеме — мы можем пойти на больший риск и ожидать успеха, в то время как схема Я, изображающая робкого человека, может привести к тому, что мы отойдем на второй план. в больших группах и избегать конфронтации. Путем корректировки нашей схемы «я» мы можем изменить ожидания от собственного поведения.

Нейроморфные вычисления с использованием архитектуры флэш-памяти NAND со схемой широтно-импульсной модуляции

Введение

В последнее время глубокие нейронные сети (ГНС) достигли превосходной производительности для различных интеллектуальных задач, таких как обработка естественного языка, компьютерное зрение и распознавание речи. (Truong et al., 2016; Nishani and Cico, 2017; Sainath et al. , 2017). Однако современные высокопроизводительные ГНС требуют огромного размера сети и огромного количества параметров и вычислительных мощностей, что требует очень быстрых и энергоемких графических процессоров (Scardapane et al., 2017; Khan et al., 2019).). Кроме того, архитектура фон Неймана приводит к огромному потреблению времени и энергии из-за узкого места между памятью и процессором. Для ускорения вычислений в нейронных сетях были предложены и разработаны нейроморфные системы, которые могут эффективно обрабатывать операцию умножения-накопления (MAC) с использованием устройств памяти (Suri et al., 2011; Jackson et al., 2013).

, 2017). Однако современные высокопроизводительные ГНС требуют огромного размера сети и огромного количества параметров и вычислительных мощностей, что требует очень быстрых и энергоемких графических процессоров (Scardapane et al., 2017; Khan et al., 2019).). Кроме того, архитектура фон Неймана приводит к огромному потреблению времени и энергии из-за узкого места между памятью и процессором. Для ускорения вычислений в нейронных сетях были предложены и разработаны нейроморфные системы, которые могут эффективно обрабатывать операцию умножения-накопления (MAC) с использованием устройств памяти (Suri et al., 2011; Jackson et al., 2013).

В предыдущих исследованиях резистивная память с произвольным доступом (RRAM) в основном использовалась в качестве синаптических устройств для реализации нейроморфной системы (Park et al., 2013; Tang et al., 2017; Andri et al., 2018; Zhou et al. , 2018 г. Гуан и Осава, 2019 г.). Однако RRAM требуют дальнейших исследований с точки зрения изменчивости характеристик клеток, надежности и интеграции селекторов для крупномасштабной интеграции (Woo and Yu, 2019). Кроме того, влияние сопротивления металлической проволоки может привести к неточной операции векторно-матричного умножения (VMM) в большом массиве (Wang et al., 2020). Кроме того, низкое отношение тока включения/выключения RRAM ограничивает пропускную способность суммарным током многих устройств RRAM (Sun et al., 2018; Yu et al., 2020). Современные алгоритмы обычно требуют огромного размера параметра. Чтобы удовлетворить этот спрос, флэш-память NAND может стать многообещающим кандидатом на роль синаптического устройства, отвечающего этому требованию. Флэш-память NAND обеспечивает сверхвысокую плотность битов для хранения огромных объемов данных и низкую стоимость изготовления в расчете на бит, и она хорошо известна как зрелая технология (Yamashita et al., 2017; Kang et al., 2019).; Хух и др., 2020). Однако флэш-память NAND обычно не использовалась в нейроморфной системе из-за особенностей структуры строки. В матричном массиве RRAM входное смещение применяется к линиям слов (WL), а выходной ток суммируется через битовые линии (BL).

Кроме того, влияние сопротивления металлической проволоки может привести к неточной операции векторно-матричного умножения (VMM) в большом массиве (Wang et al., 2020). Кроме того, низкое отношение тока включения/выключения RRAM ограничивает пропускную способность суммарным током многих устройств RRAM (Sun et al., 2018; Yu et al., 2020). Современные алгоритмы обычно требуют огромного размера параметра. Чтобы удовлетворить этот спрос, флэш-память NAND может стать многообещающим кандидатом на роль синаптического устройства, отвечающего этому требованию. Флэш-память NAND обеспечивает сверхвысокую плотность битов для хранения огромных объемов данных и низкую стоимость изготовления в расчете на бит, и она хорошо известна как зрелая технология (Yamashita et al., 2017; Kang et al., 2019).; Хух и др., 2020). Однако флэш-память NAND обычно не использовалась в нейроморфной системе из-за особенностей структуры строки. В матричном массиве RRAM входное смещение применяется к линиям слов (WL), а выходной ток суммируется через битовые линии (BL). Таким образом, VMM входного напряжения, подаваемого на WL, и проводимость RRAM могут быть легко реализованы. Однако в архитектуре флэш-памяти NAND WL и исходная строка (SL) совместно используются строками NAND в одном блоке. Кроме того, к выбранному слою и невыбранным слоям применяются смещение считывания и смещение пропускания, соответственно, для считывания тока ячеек И-НЕ выбранного слоя. Поэтому было сочтено сложным реализовать VMM в архитектуре флэш-памяти NAND.

Таким образом, VMM входного напряжения, подаваемого на WL, и проводимость RRAM могут быть легко реализованы. Однако в архитектуре флэш-памяти NAND WL и исходная строка (SL) совместно используются строками NAND в одном блоке. Кроме того, к выбранному слою и невыбранным слоям применяются смещение считывания и смещение пропускания, соответственно, для считывания тока ячеек И-НЕ выбранного слоя. Поэтому было сочтено сложным реализовать VMM в архитектуре флэш-памяти NAND.

В этой статье предлагается новая нейроморфная архитектура для квантованной нейронной сети (QNN), использующая флэш-память NAND со схемой широтно-импульсной модуляции (PWM). Наша схема реализует нейроморфную систему высокой плотности, поскольку две ячейки И-НЕ с восемью уровнями тока (3-битные) используются как одно синаптическое устройство, а схема ШИМ может представлять аналоговые входные значения. Кроме того, наша схема может обрабатывать MAC аналогового входного значения и 4-битного веса всего за один входной шаг, что значительно снижает энергопотребление и нагрузку на периферийные схемы, необходимые в архитектурах с цифровым дизайном. Использование насыщенных вольт-амперных характеристик ячеек И-НЕ решает проблему, возникающую из-за сопротивления проходных ячеек, где применяется проходное смещение, и металлической проволоки. Кроме того, исследуется влияние обучения квантованию (QT) на точность вывода по сравнению с квантованием после обучения (PTQ). Наконец, мы показываем, что достаточно низкая дисперсия тока синаптических устройств, полученная методом чтения-проверки-записи (RVW), достигает удовлетворительной точности.

Использование насыщенных вольт-амперных характеристик ячеек И-НЕ решает проблему, возникающую из-за сопротивления проходных ячеек, где применяется проходное смещение, и металлической проволоки. Кроме того, исследуется влияние обучения квантованию (QT) на точность вывода по сравнению с квантованием после обучения (PTQ). Наконец, мы показываем, что достаточно низкая дисперсия тока синаптических устройств, полученная методом чтения-проверки-записи (RVW), достигает удовлетворительной точности.

Материалы и методы

Нейроморфная система с использованием флэш-памяти NAND

На рис. 1 схематически показана схема работы нейроморфной системы, использующей трехмерную (3D) флэш-память NAND со схемами ШИМ. Входные напряжения с регулируемой шириной импульса от схем ШИМ накладываются на линии выбора строки (SSL), где ток ячейки добавляется в BL, как показано на рисунке 1A. Клетки NAND в k th WL представляют синапсы в k -й -й синаптический слой нейронной сети показан на рисунке 1В. Смещение чтения ( V чтение ) и смещение пропуска ( V PASS ) накладываются на выбранный WL и невыбранный WL, соответственно, как показано на рисунке 1C. Когда V считывание накладываются на WL последовательно вдоль синаптической цепочки, последовательно генерируется выход каждого постсинаптического нейрона. Ячейки подключены к выбранному весу хранилища WL, и каждый вес определяет строковый ток каждой строки. В предлагаемой схеме входное напряжение одновременно подается на все ТСС. Предлагаемая схема работы отличается от стандартной архитектуры флэш-памяти NAND, что можно сравнить с таблицей 1. Входное смещение, соответствующее активации нейронов, применяется к SSL, а текущая сумма считывается через BL в предлагаемой схеме работы. С другой стороны, ячейка, выбранная по входному адресу, считывается через BL в обычной флэш-памяти NAND. Кроме того, в предлагаемой схеме SSL одновременно смещаются входным напряжением, тогда как смещение чтения накладывается последовательно на каждый SSL в обычной флэш-памяти NAND.

Смещение чтения ( V чтение ) и смещение пропуска ( V PASS ) накладываются на выбранный WL и невыбранный WL, соответственно, как показано на рисунке 1C. Когда V считывание накладываются на WL последовательно вдоль синаптической цепочки, последовательно генерируется выход каждого постсинаптического нейрона. Ячейки подключены к выбранному весу хранилища WL, и каждый вес определяет строковый ток каждой строки. В предлагаемой схеме входное напряжение одновременно подается на все ТСС. Предлагаемая схема работы отличается от стандартной архитектуры флэш-памяти NAND, что можно сравнить с таблицей 1. Входное смещение, соответствующее активации нейронов, применяется к SSL, а текущая сумма считывается через BL в предлагаемой схеме работы. С другой стороны, ячейка, выбранная по входному адресу, считывается через BL в обычной флэш-памяти NAND. Кроме того, в предлагаемой схеме SSL одновременно смещаются входным напряжением, тогда как смещение чтения накладывается последовательно на каждый SSL в обычной флэш-памяти NAND. Таким образом, эта схема значительно снижает задержку по сравнению с обычной технологией флэш-памяти NAND. Выходной ток в обеих схемах считывается через ШД. Кроме того, предлагаемая синаптическая архитектура, использующая флэш-память NAND, отличается от массива перекладин RRAM. В матричной матрице RRAM входное смещение подается на WL, а выходной ток суммируется через BL. Массив ячеек NAND состоит из цепочек ячеек, и каждая цепочка ячеек имеет несколько последовательно соединенных ячеек. В массиве ячеек NAND WL и SL совместно используются строками NAND в одном и том же блоке флэш-памяти NAND. Кроме того, чтобы включить невыбранные ячейки, передайте смещение ( V PASS ) следует применять к WL невыбранных ячеек. Поэтому в предлагаемой синаптической архитектуре вход подается на SSL, а выходной ток считывается в BL. Кроме того, клетки в слое k th в цепочках флэш-памяти NAND представляют синапсы в слое синапсов слоя k th в нейронных сетях.

Таким образом, эта схема значительно снижает задержку по сравнению с обычной технологией флэш-памяти NAND. Выходной ток в обеих схемах считывается через ШД. Кроме того, предлагаемая синаптическая архитектура, использующая флэш-память NAND, отличается от массива перекладин RRAM. В матричной матрице RRAM входное смещение подается на WL, а выходной ток суммируется через BL. Массив ячеек NAND состоит из цепочек ячеек, и каждая цепочка ячеек имеет несколько последовательно соединенных ячеек. В массиве ячеек NAND WL и SL совместно используются строками NAND в одном и том же блоке флэш-памяти NAND. Кроме того, чтобы включить невыбранные ячейки, передайте смещение ( V PASS ) следует применять к WL невыбранных ячеек. Поэтому в предлагаемой синаптической архитектуре вход подается на SSL, а выходной ток считывается в BL. Кроме того, клетки в слое k th в цепочках флэш-памяти NAND представляют синапсы в слое синапсов слоя k th в нейронных сетях. Обратите внимание, что предложенная схема работы может быть применена как к архитектуре флэш-памяти 2D, так и к 3D NAND.

Обратите внимание, что предложенная схема работы может быть применена как к архитектуре флэш-памяти 2D, так и к 3D NAND.

Рис. 1. (A) Схема работы массива синаптических строк, использующего флэш-память NAND со схемами ШИМ. (B) Принципиальная схема нейронных сетей. (C) Импульсная диаграмма, примененная к WL со временем.

Таблица 1. Сравнение предлагаемой схемы работы с традиционной флэш-памятью NAND.

На рис. 2 представлена работа VMM с использованием массива строк и нейронных цепей. В нейроморфной системе вес и вход в алгоритме DNN представлены соответственно проводимостью и входным напряжением синаптических устройств. В алгоритме DNN выход взвешенной суммы линейно увеличивается с входом, как показано в уравнении;

Рис. 2. (A) Схематическая диаграмма массива синаптических струн, состоящего из синапсов с положительным весом ( G + ) и синапсов с отрицательным весом ( G – ). (B) Импульсная диаграмма схемы работы и напряжения конденсатора во времени. (C) Напряжение конденсатора ( V C ) с разницей I EVEN и I НЕЧЕТНЫЙ .

(B) Импульсная диаграмма схемы работы и напряжения конденсатора во времени. (C) Напряжение конденсатора ( V C ) с разницей I EVEN и I НЕЧЕТНЫЙ .

O=∑WX(1)

, где O , W и X представляют взвешенную сумму выхода, веса и входа соответственно. В нейроморфной системе обычно предполагается, что синаптические устройства имеют линейную характеристику тока ( I ) по отношению к напряжению ( V ) (Kim T. et al., 2017). Если синаптические устройства имеют линейные характеристики ВАХ , амплитуда входного сигнала в модели ГНС может быть просто представлена амплитудой входного напряжения синаптических устройств. Затем взвешенный суммарный ток представляется произведением входного напряжения и проводимости синаптических устройств, как показано в уравнении;

I=∑GV(2)

, где I , G и V представляют взвешенную сумму тока, проводимости и входного напряжения устройств соответственно. С другой стороны, ячейка флэш-памяти NAND имеет нелинейные характеристики I-V (Lee et al., 2018, 2019a), что означает, что выходной ток имеет нелинейную зависимость от входного напряжения. Таким образом, аналоговая амплитуда входного импульса не может представлять амплитуду входного сигнала в алгоритме DNN (Lee et al., 2019).б). Для решения проблемы нелинейности ВАХ ячеек И-НЕ предлагается схема ШИМ. В этой схеме амплитуда входного импульса фиксирована, тогда как ширина входного импульса изменяется пропорционально амплитуде входного сигнала в алгоритме DNN. Затем выходная взвешенная сумма представлена количеством заряда, накопленного в нейронных цепях, тогда как входное напряжение подается, как показано в уравнении;

С другой стороны, ячейка флэш-памяти NAND имеет нелинейные характеристики I-V (Lee et al., 2018, 2019a), что означает, что выходной ток имеет нелинейную зависимость от входного напряжения. Таким образом, аналоговая амплитуда входного импульса не может представлять амплитуду входного сигнала в алгоритме DNN (Lee et al., 2019).б). Для решения проблемы нелинейности ВАХ ячеек И-НЕ предлагается схема ШИМ. В этой схеме амплитуда входного импульса фиксирована, тогда как ширина входного импульса изменяется пропорционально амплитуде входного сигнала в алгоритме DNN. Затем выходная взвешенная сумма представлена количеством заряда, накопленного в нейронных цепях, тогда как входное напряжение подается, как показано в уравнении;

Q=V∑GT(3)

, где Q , V , G и T представляют взвешенный суммарный заряд, постоянную амплитуду входного импульса, проводимость устройства и ширину входного импульса соответственно. Следовательно, взвешенная сумма в модели DNN может быть правильно выполнена в нейроморфных системах с использованием схемы PWM, несмотря на нелинейные характеристики сотовых устройств. Кроме того, эта схема хорошо подходит для традиционной архитектуры флэш-памяти NAND. Две соседние ячейки И-НЕ используются для одного синаптического устройства для представления значения отрицательного веса. Учитывая отрицательный вес, заряд, накопленный в цепи нейрона, может быть представлен уравнением;

Кроме того, эта схема хорошо подходит для традиционной архитектуры флэш-памяти NAND. Две соседние ячейки И-НЕ используются для одного синаптического устройства для представления значения отрицательного веса. Учитывая отрицательный вес, заряд, накопленный в цепи нейрона, может быть представлен уравнением;

Q=V∑T(G+-G-)(4)